proj3

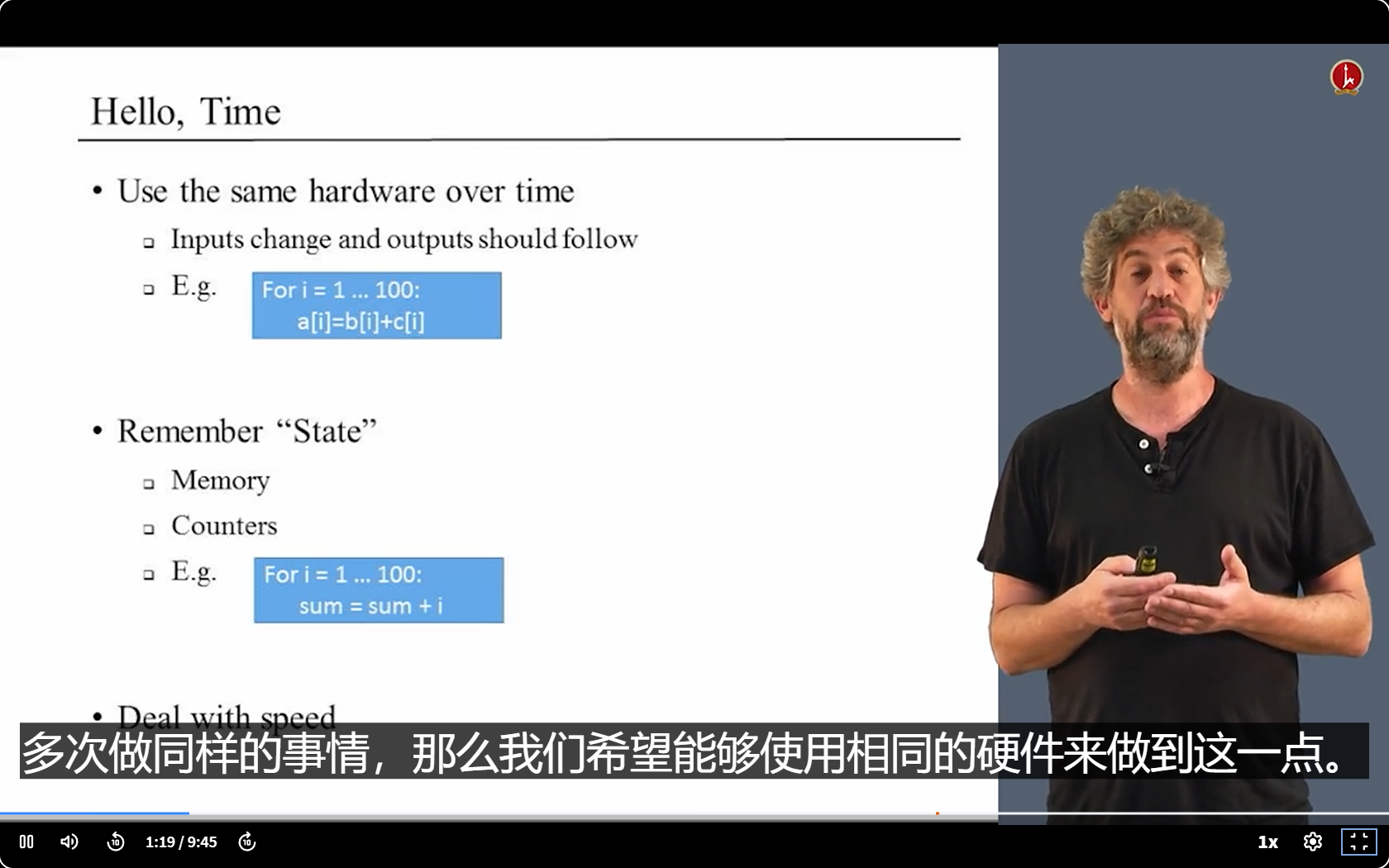

3.1 Sequential Logic(逻辑时序)

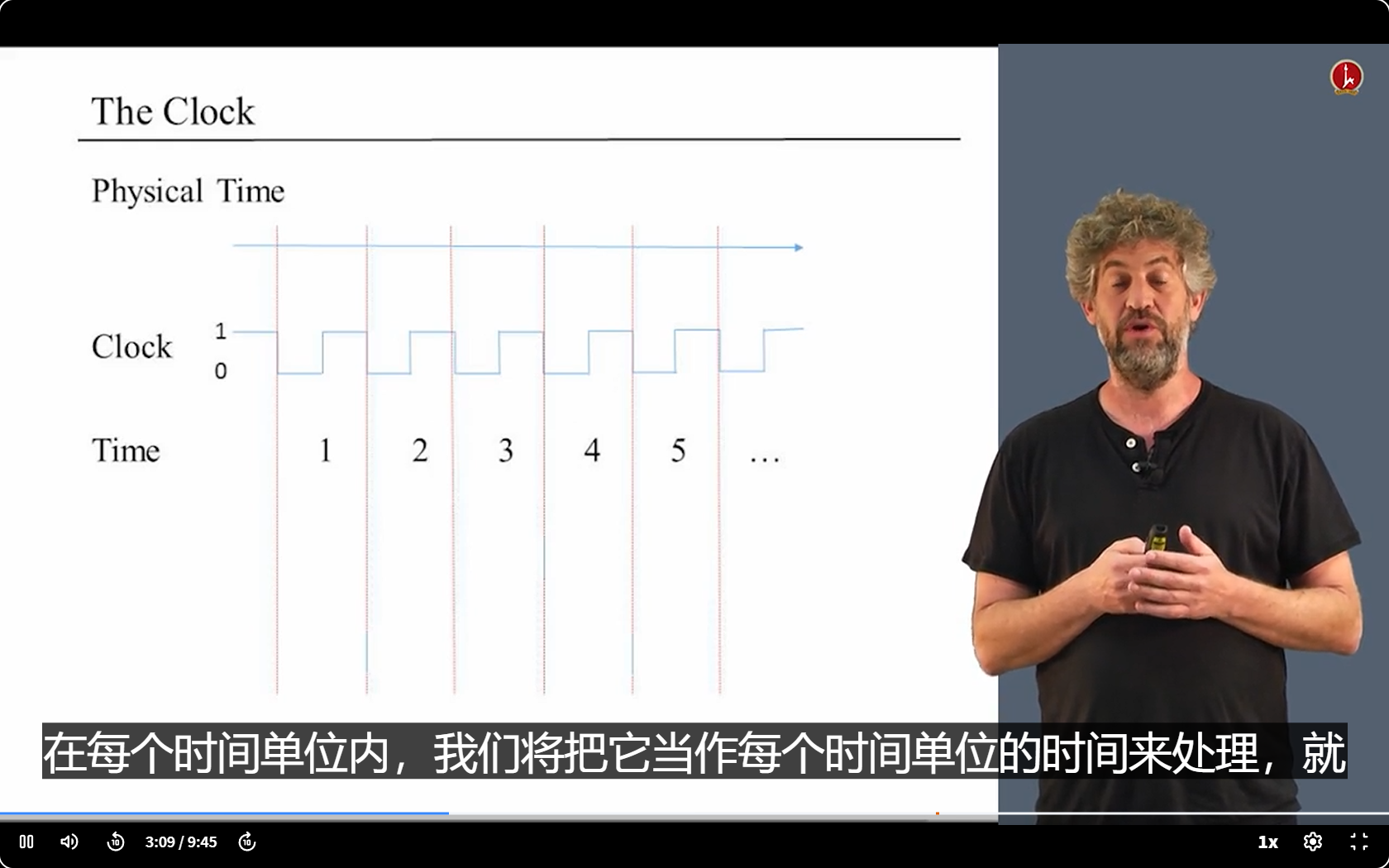

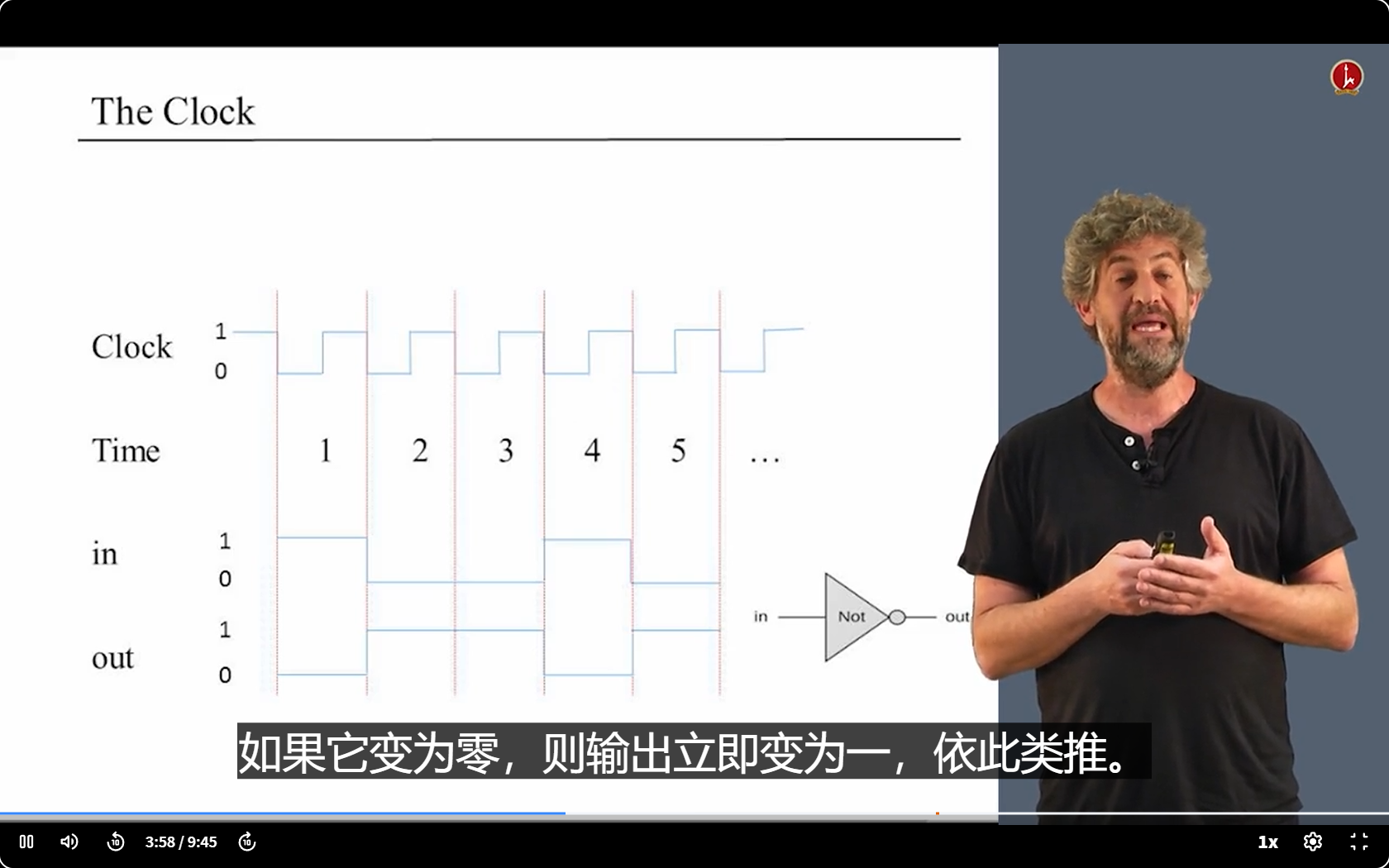

The Clock

⭐

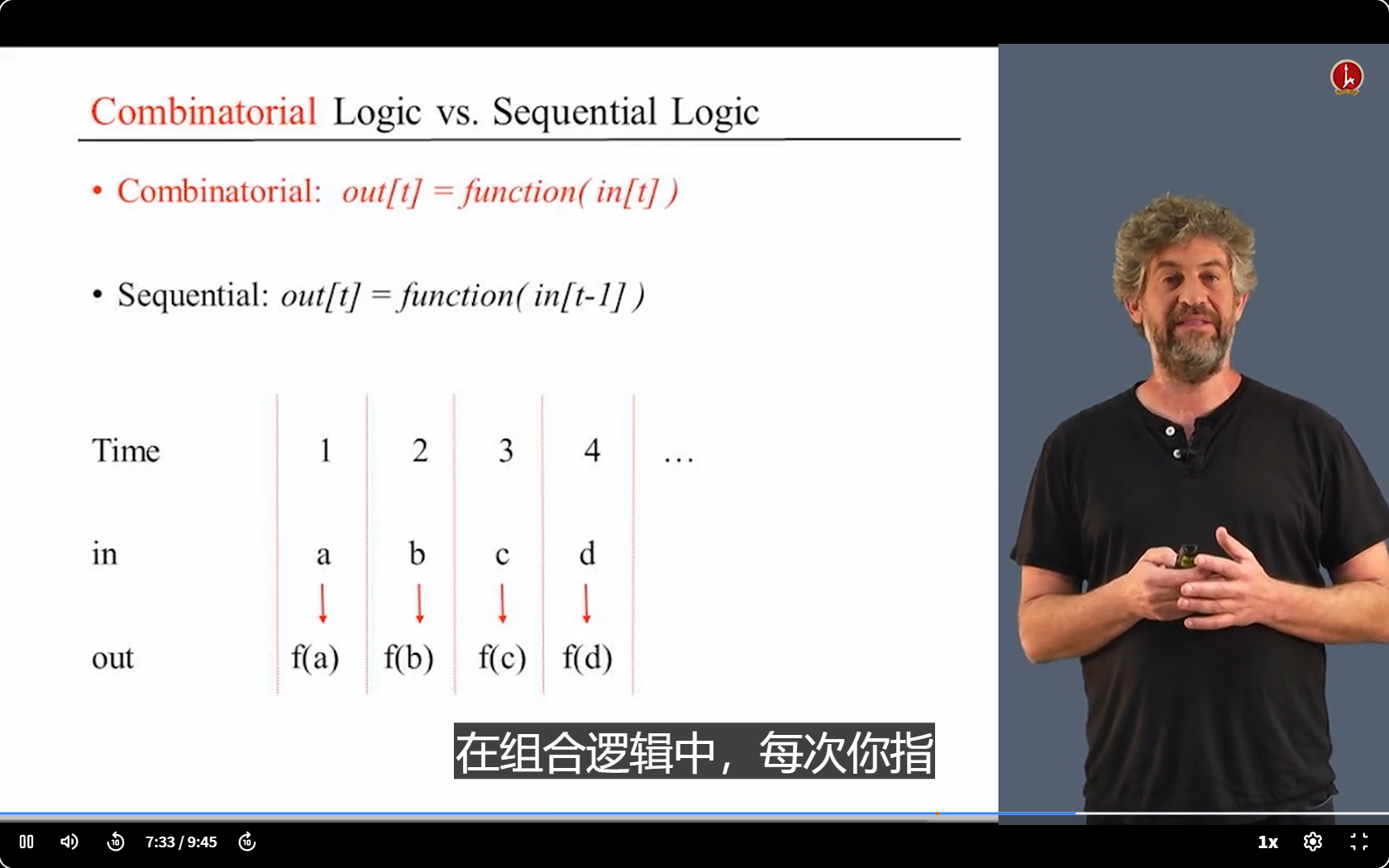

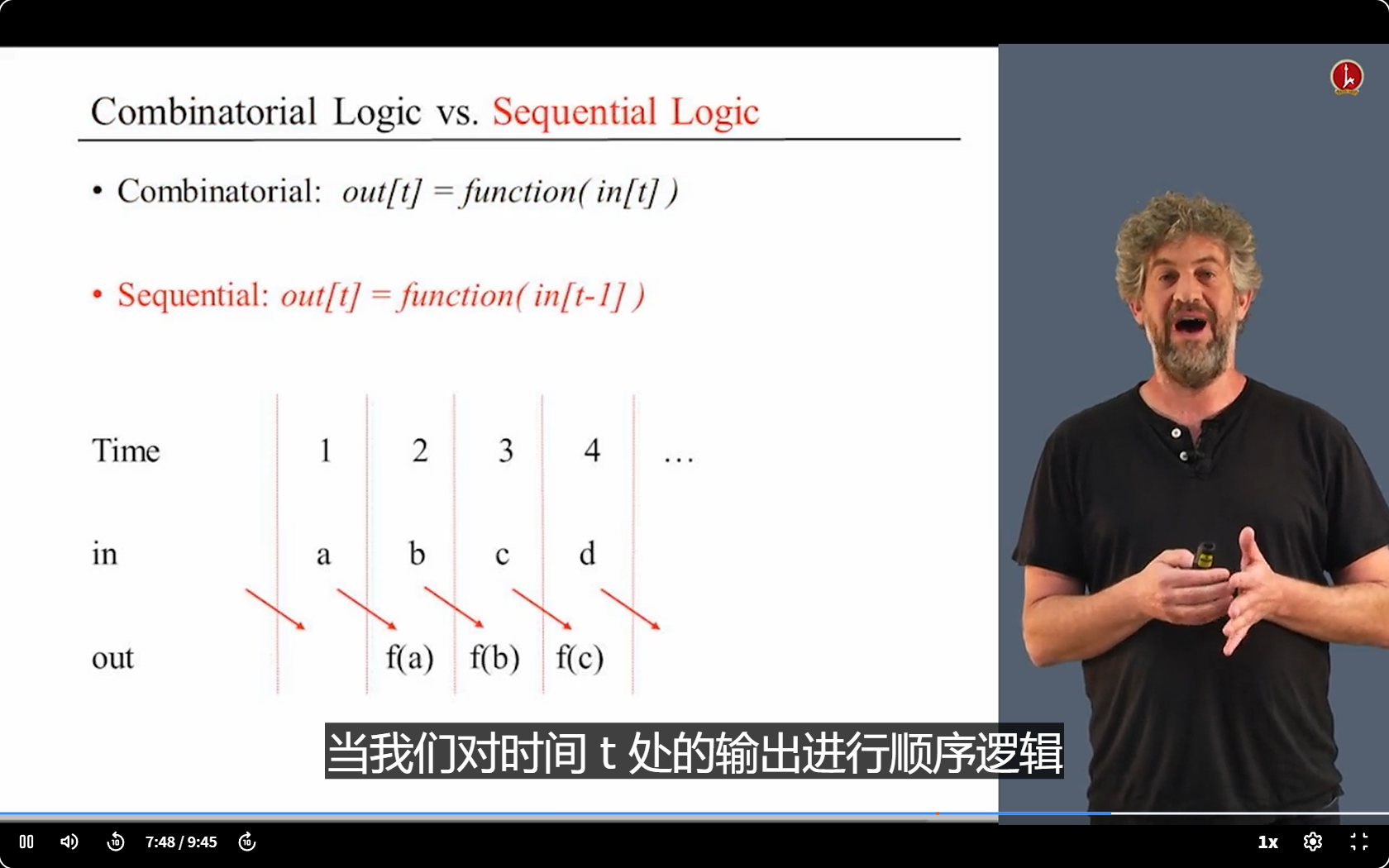

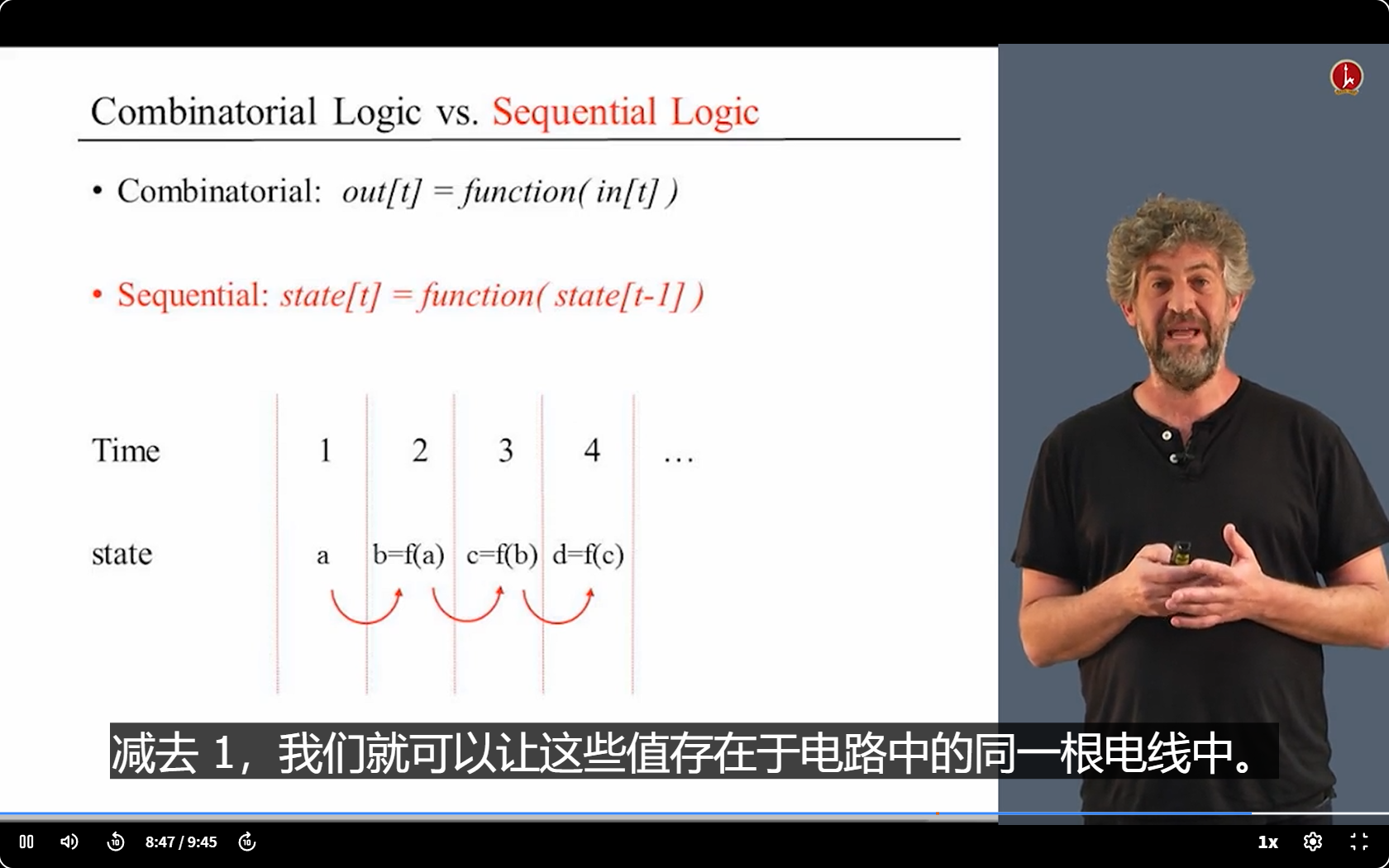

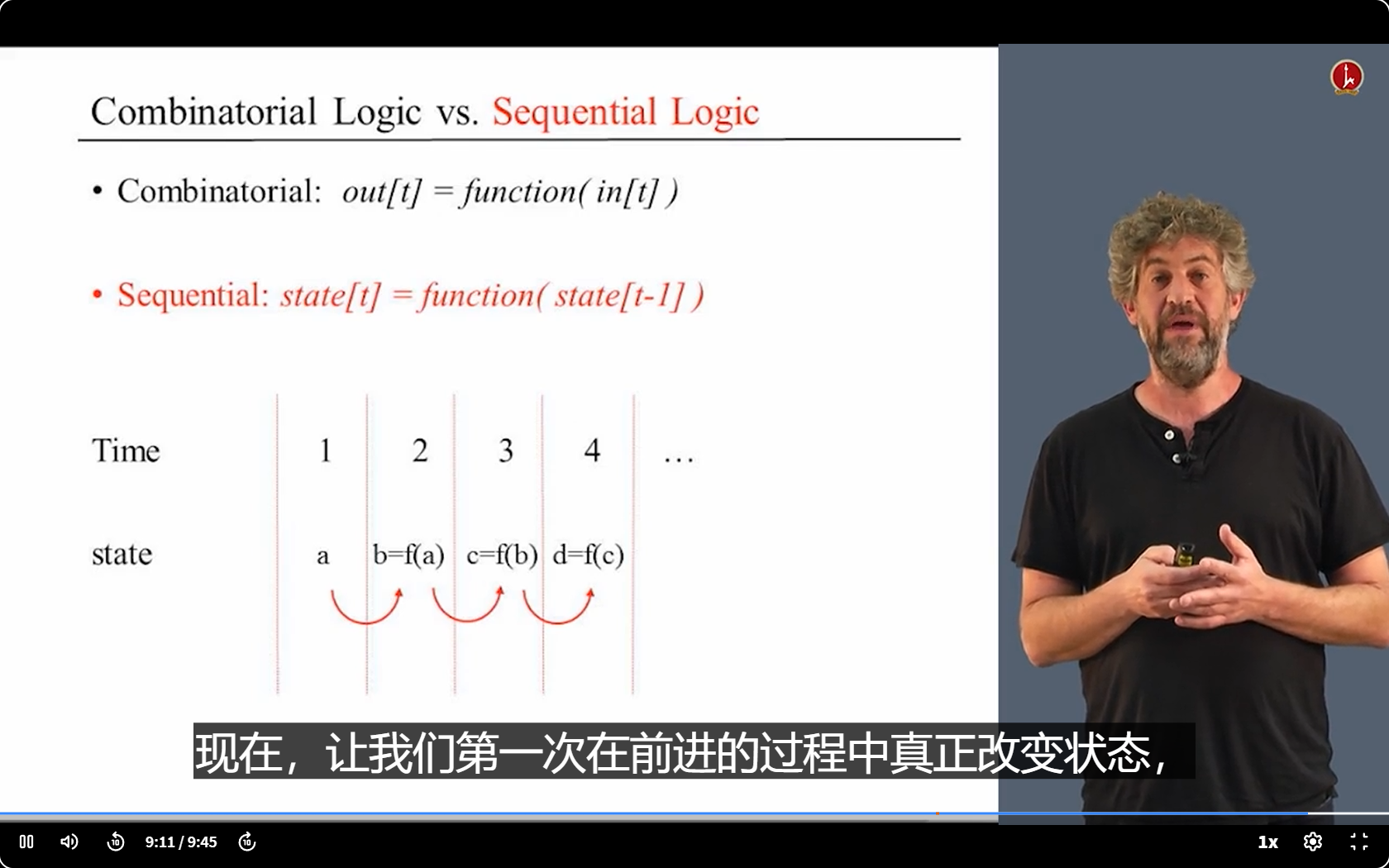

Combinatorial Logic vs. Sequential Logic

3.2 Flip Flops 触发器

制作:允许上一步操作的芯片

⭐

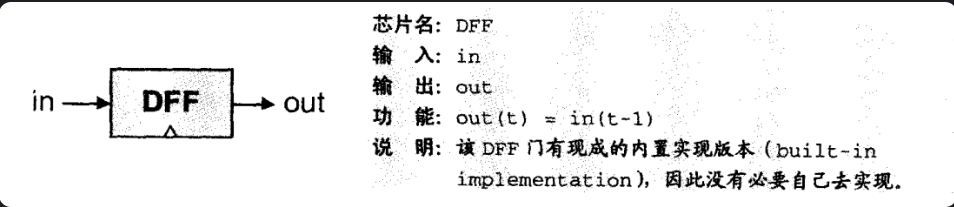

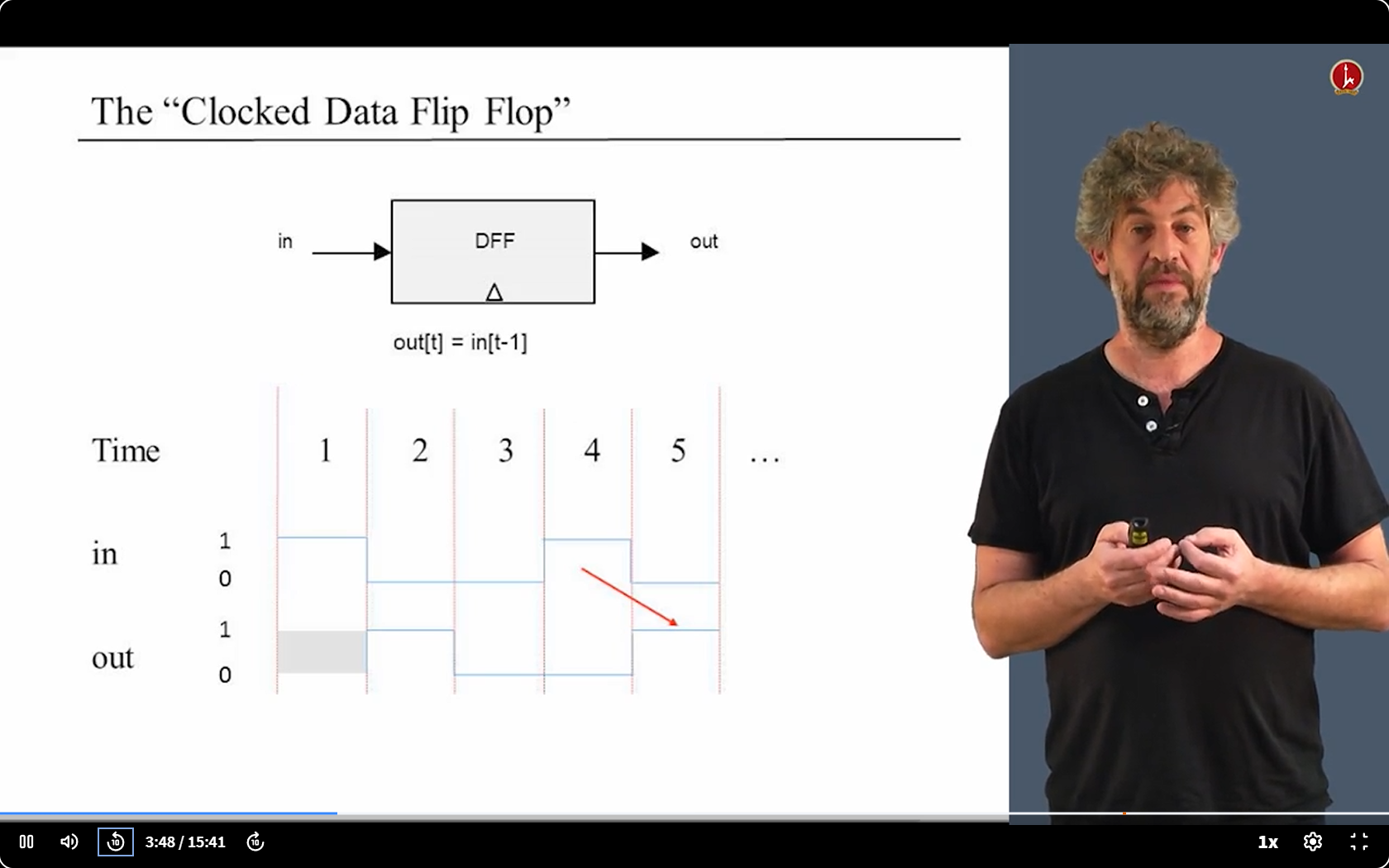

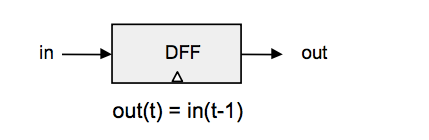

D 触发器

换句话说,DFF 简单地将前一个时间周期的输入值作为当前周期的输出。𝑜𝑢𝑡(𝑡)=𝑖𝑛(𝑡−1)

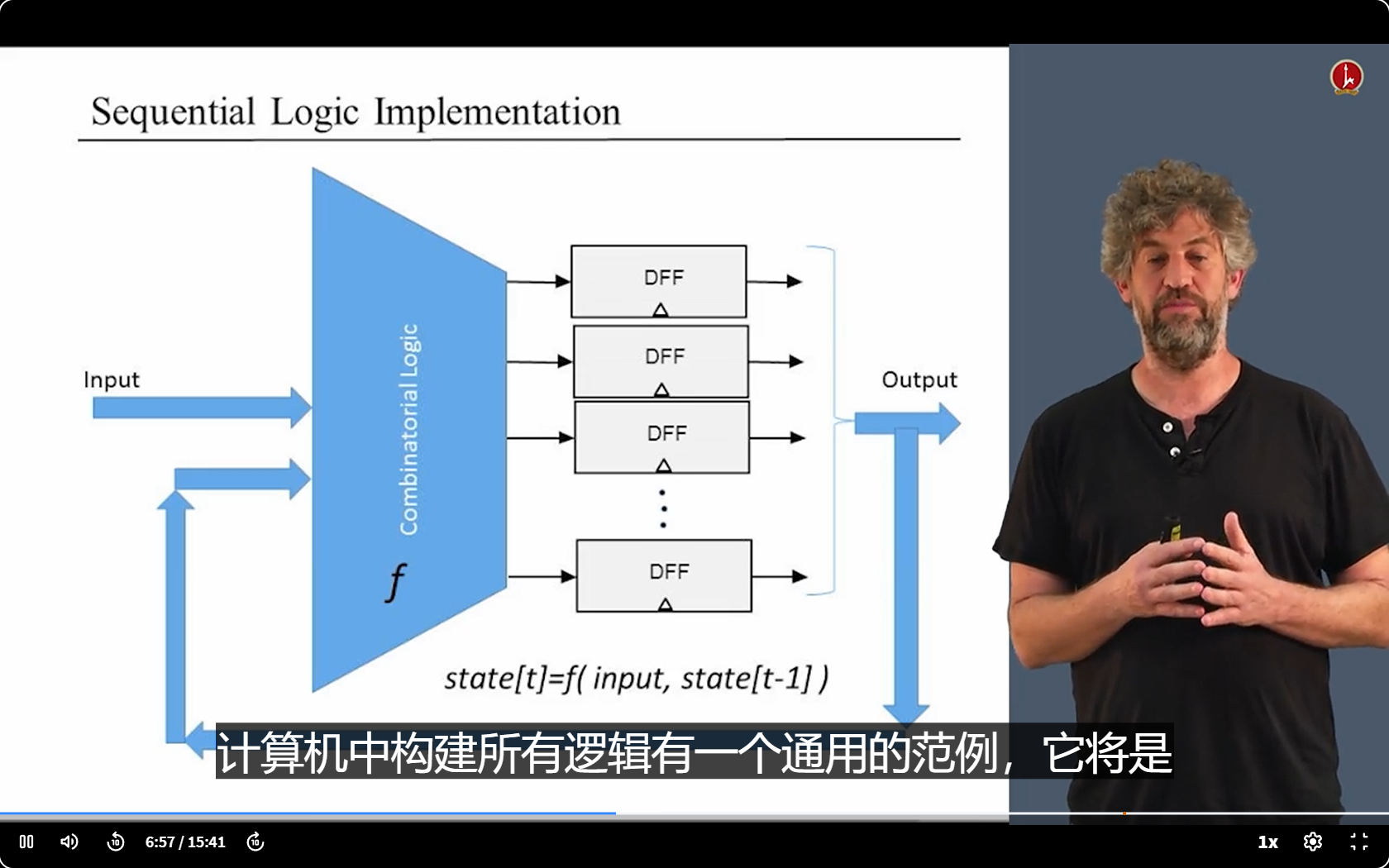

时序逻辑的原理

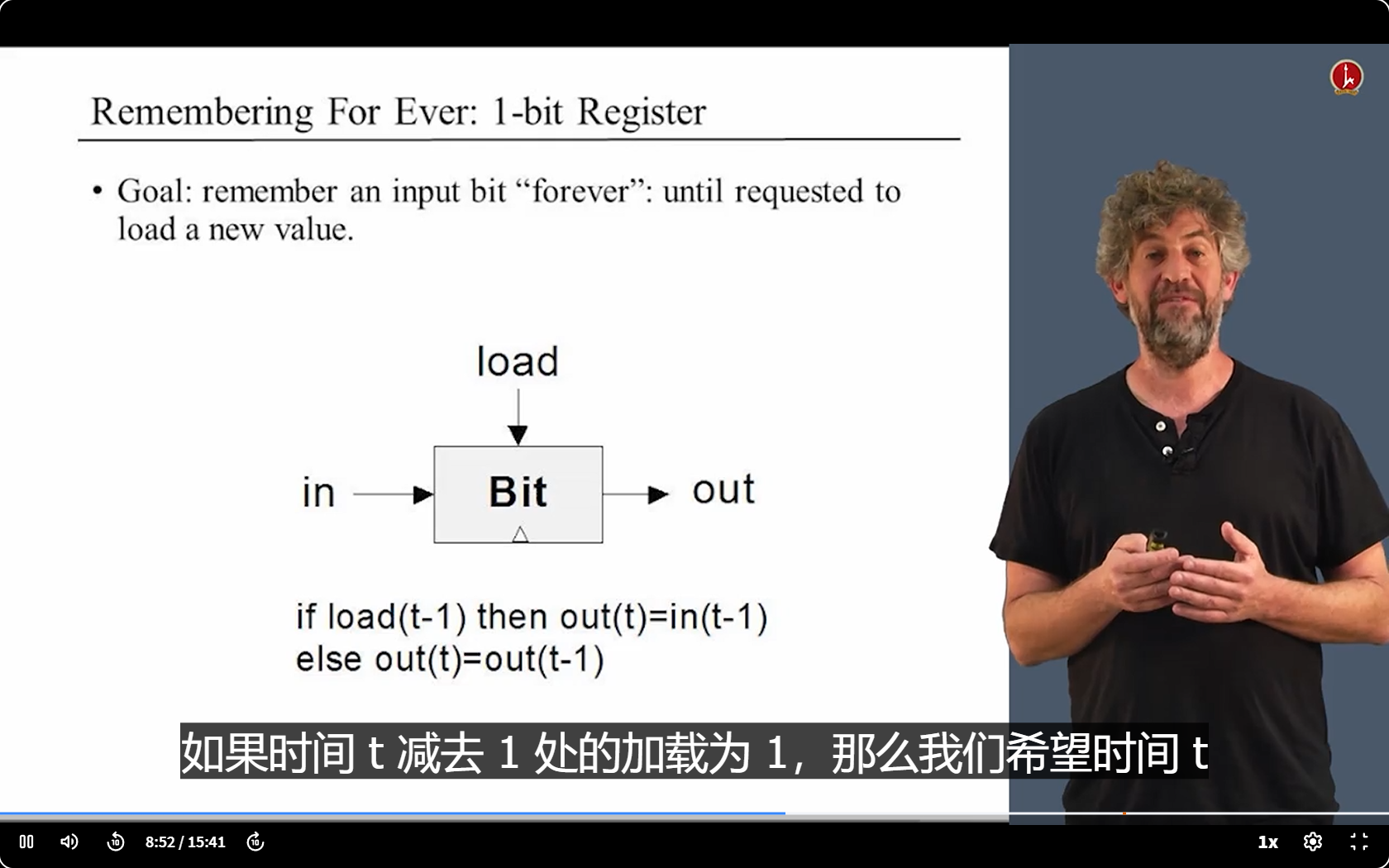

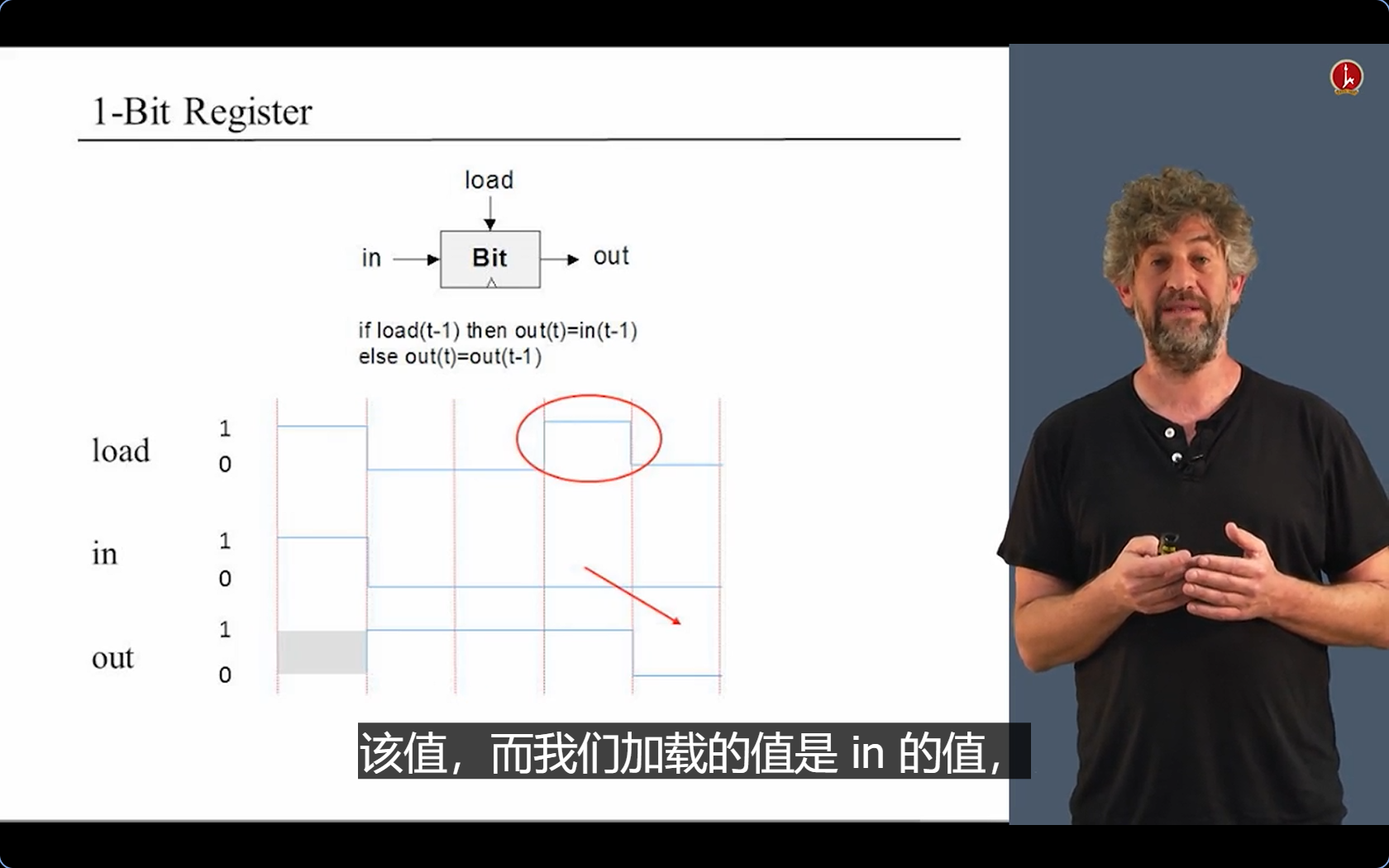

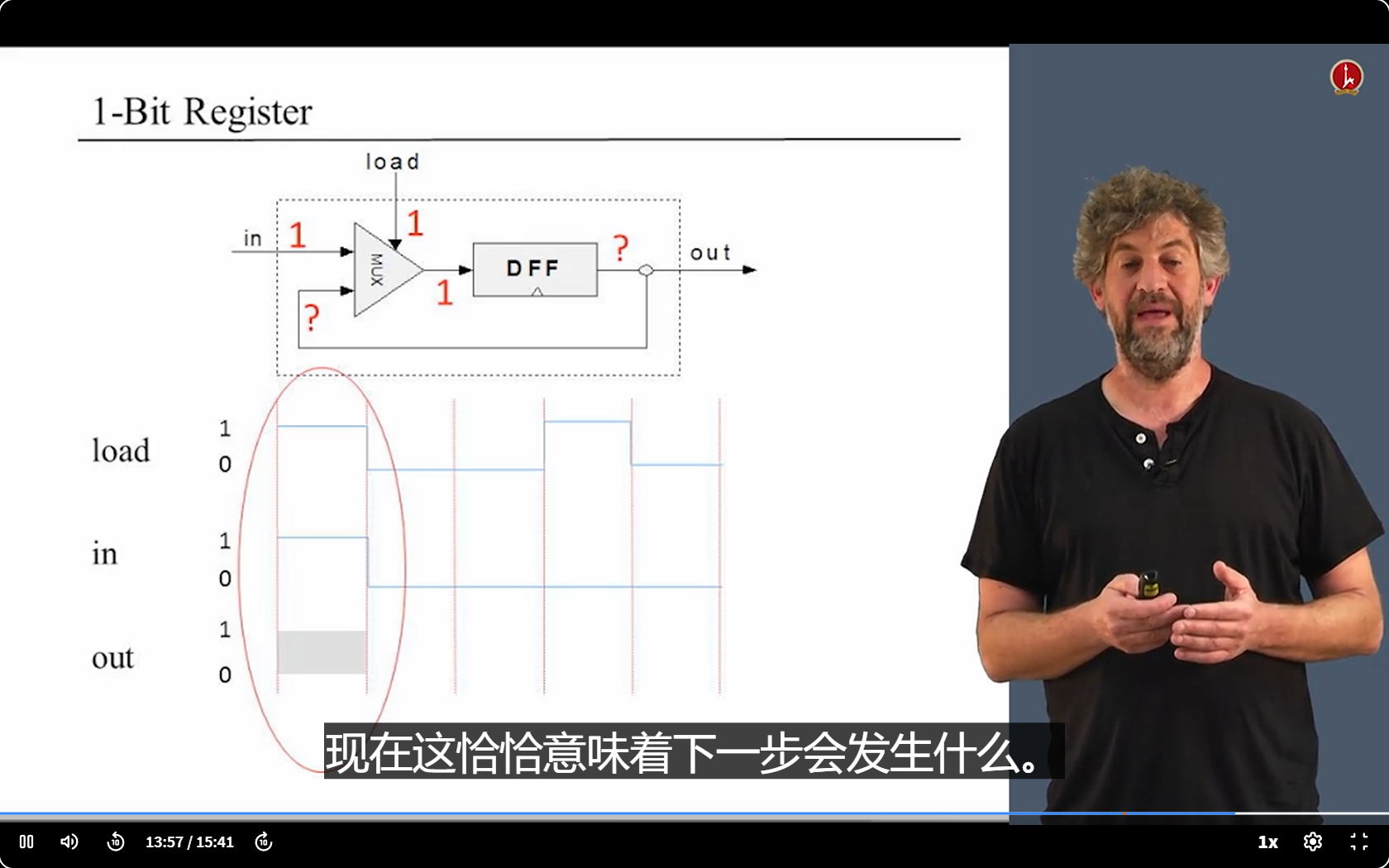

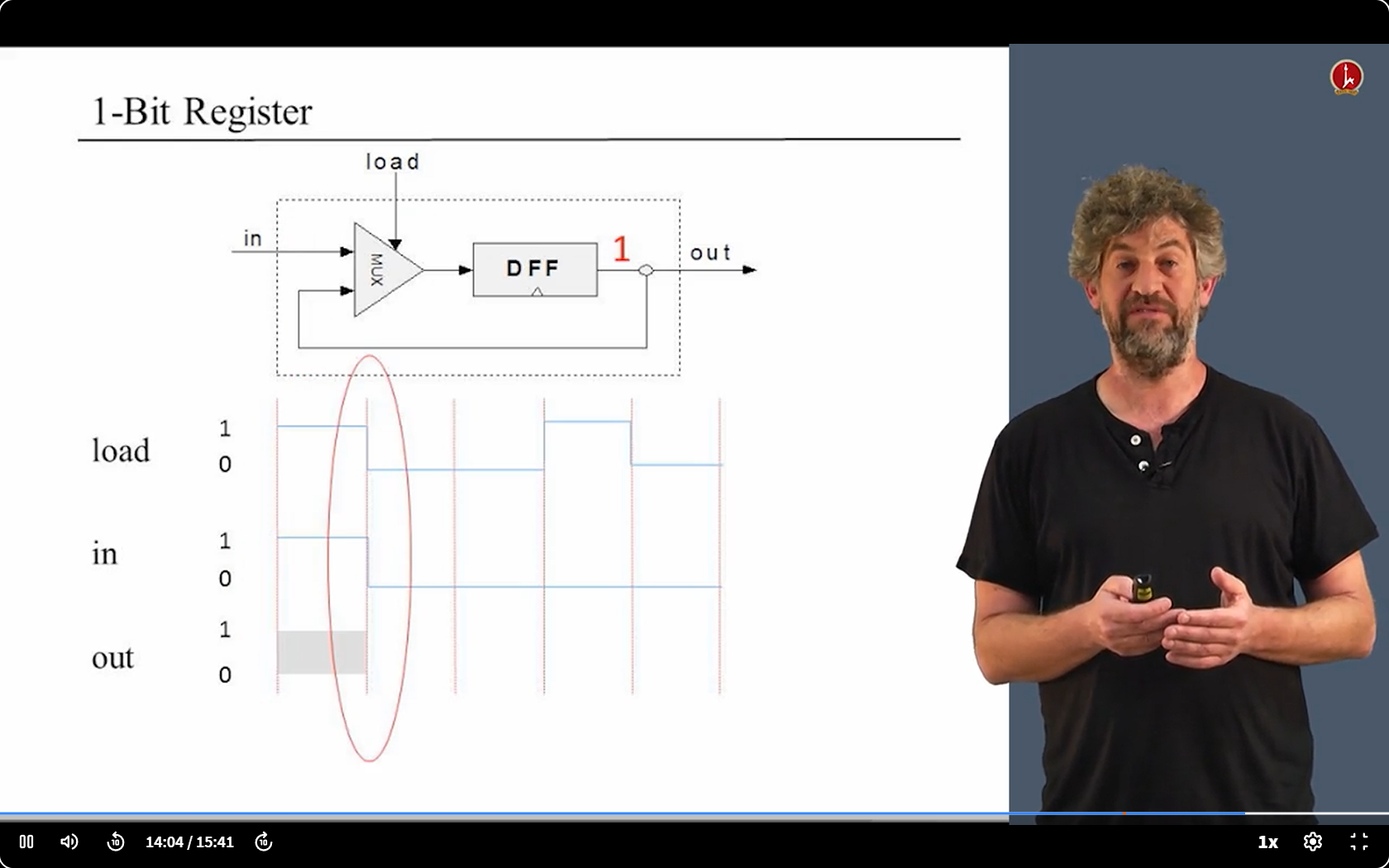

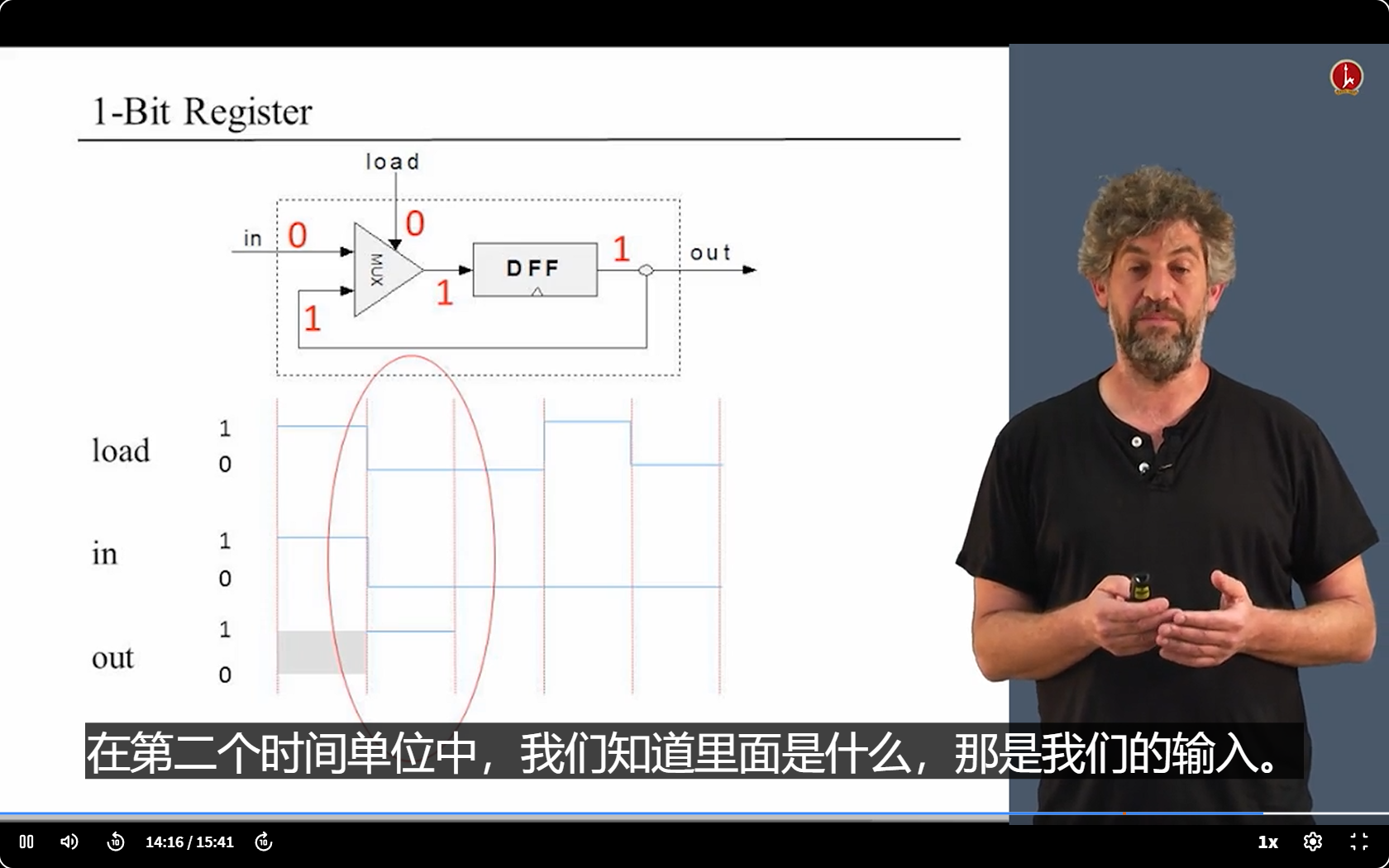

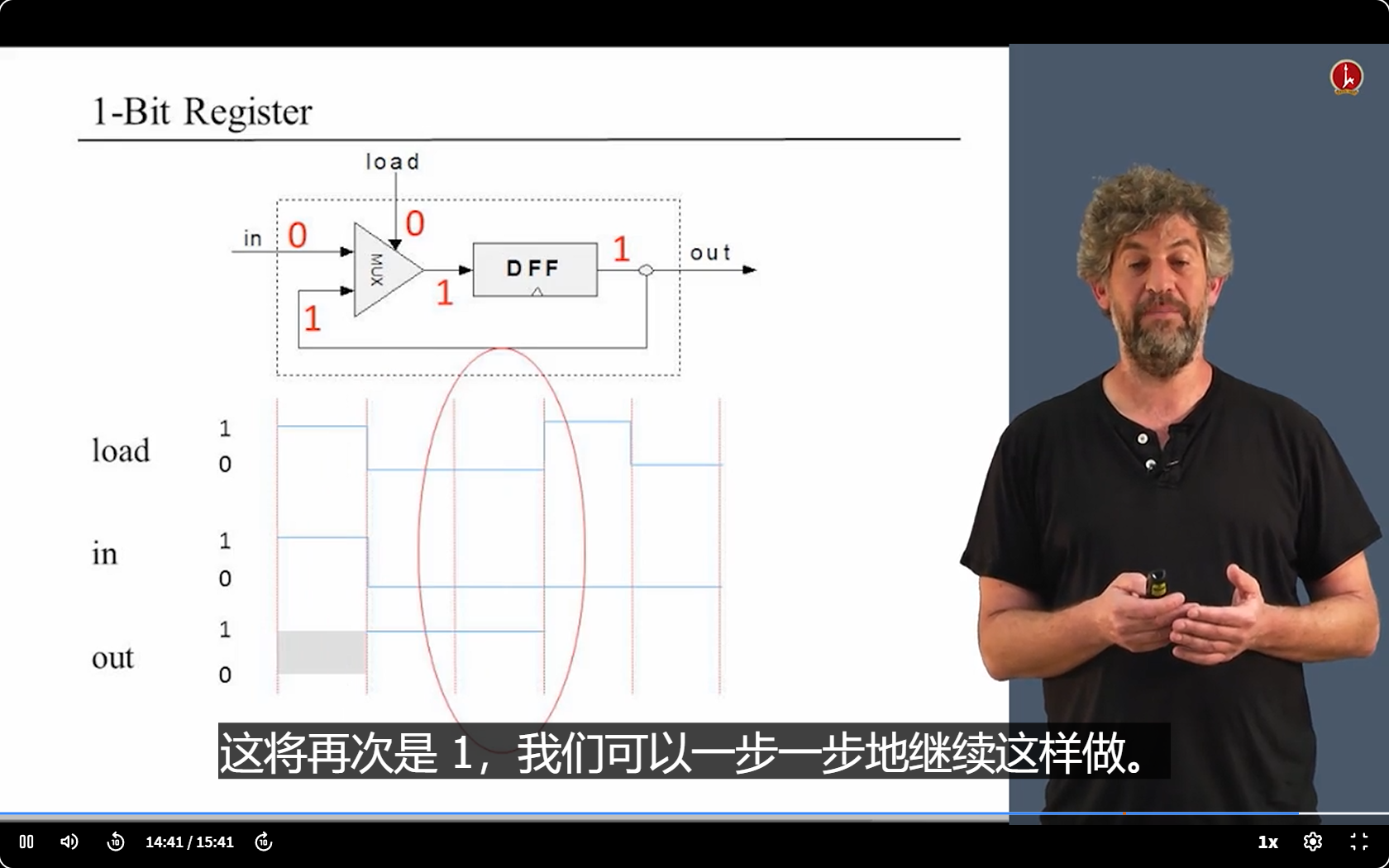

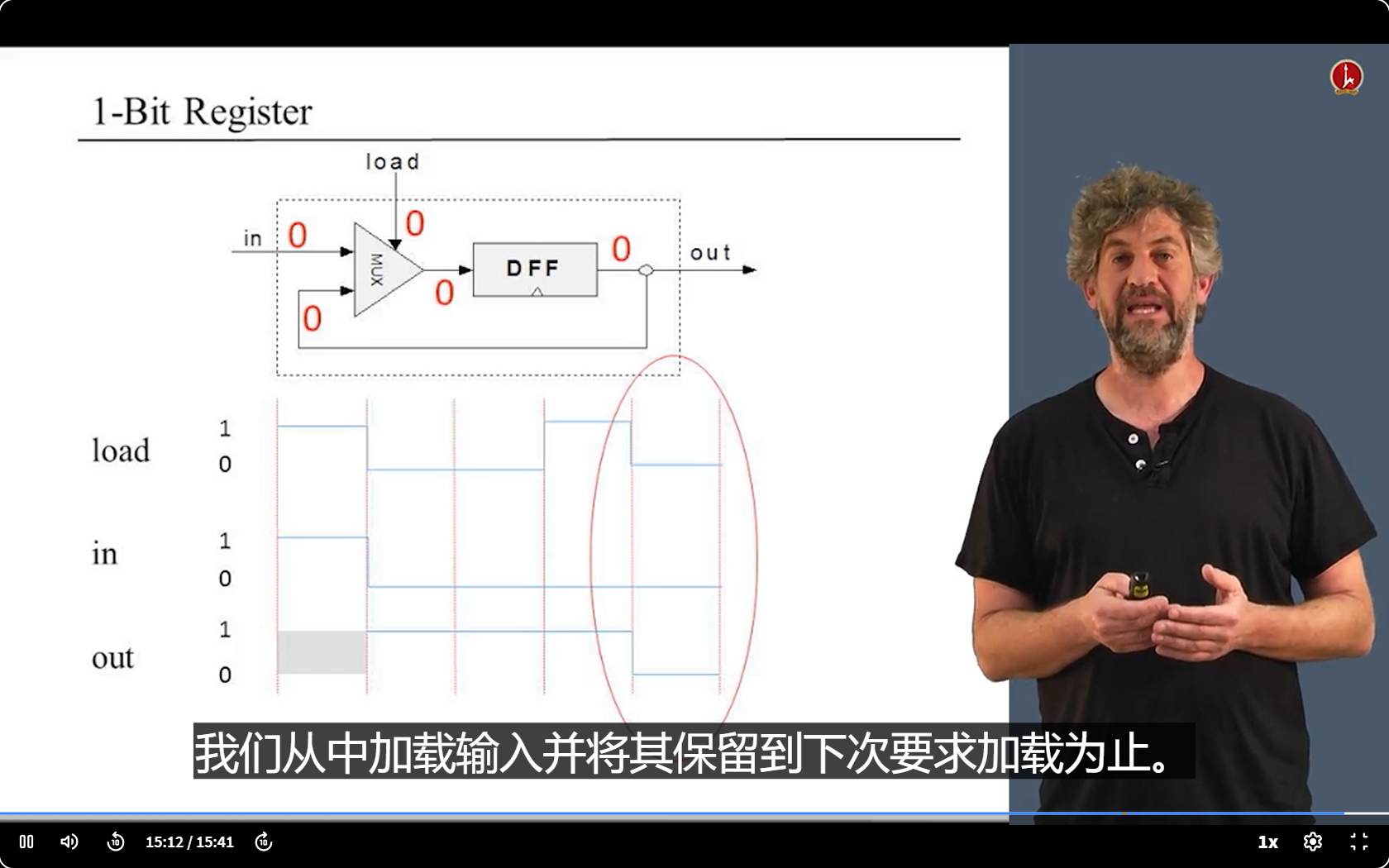

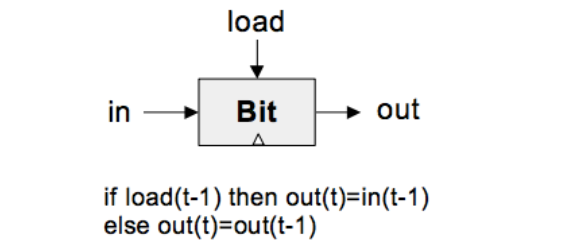

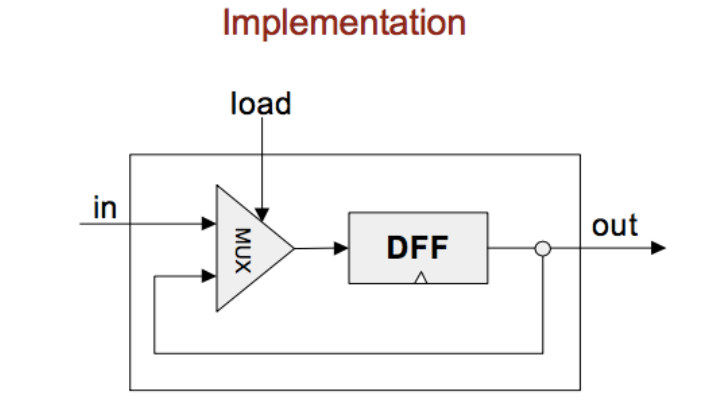

寄存器 Bit

【寄存器(也)是一种常用的时序逻辑电路】

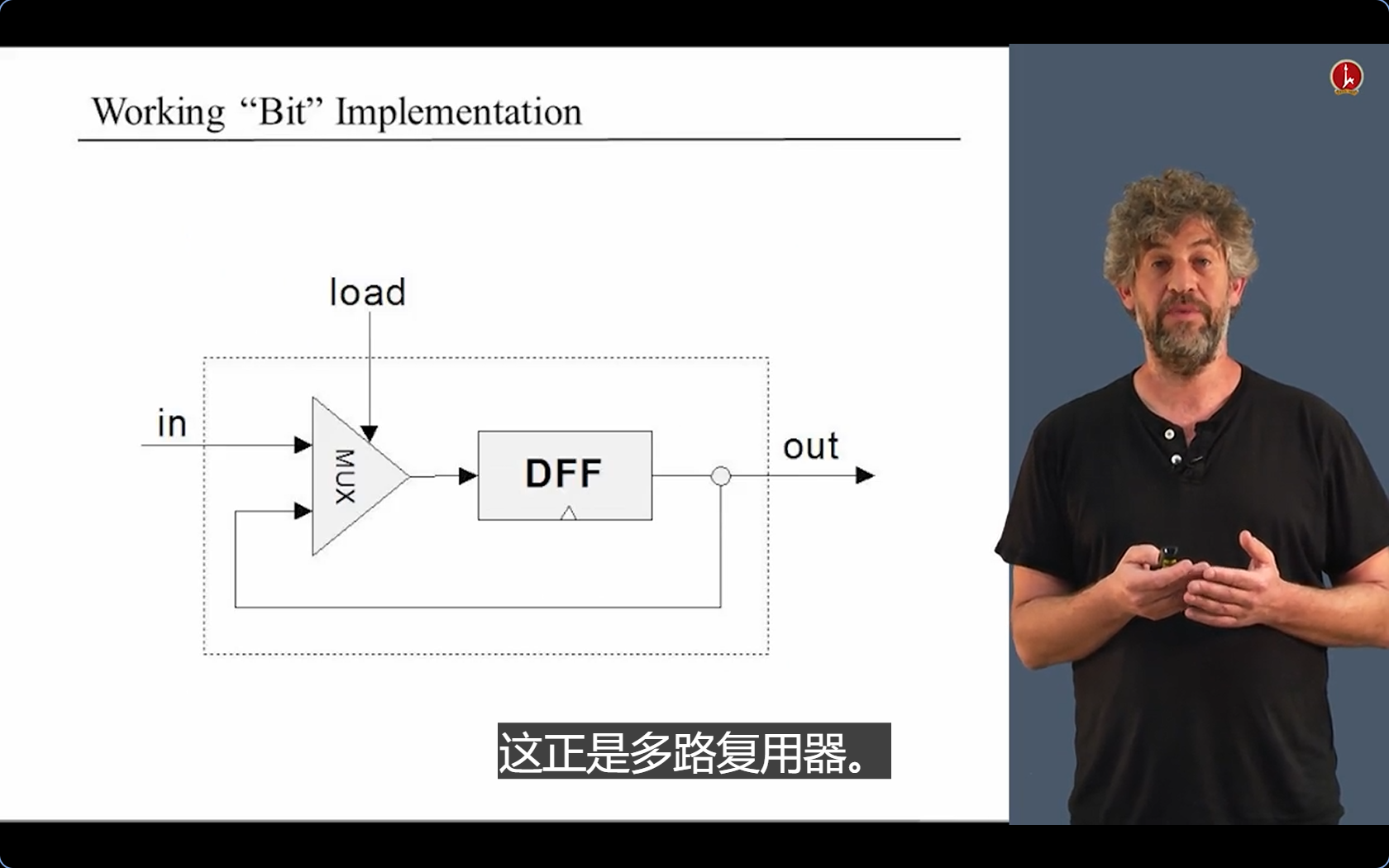

implement

show

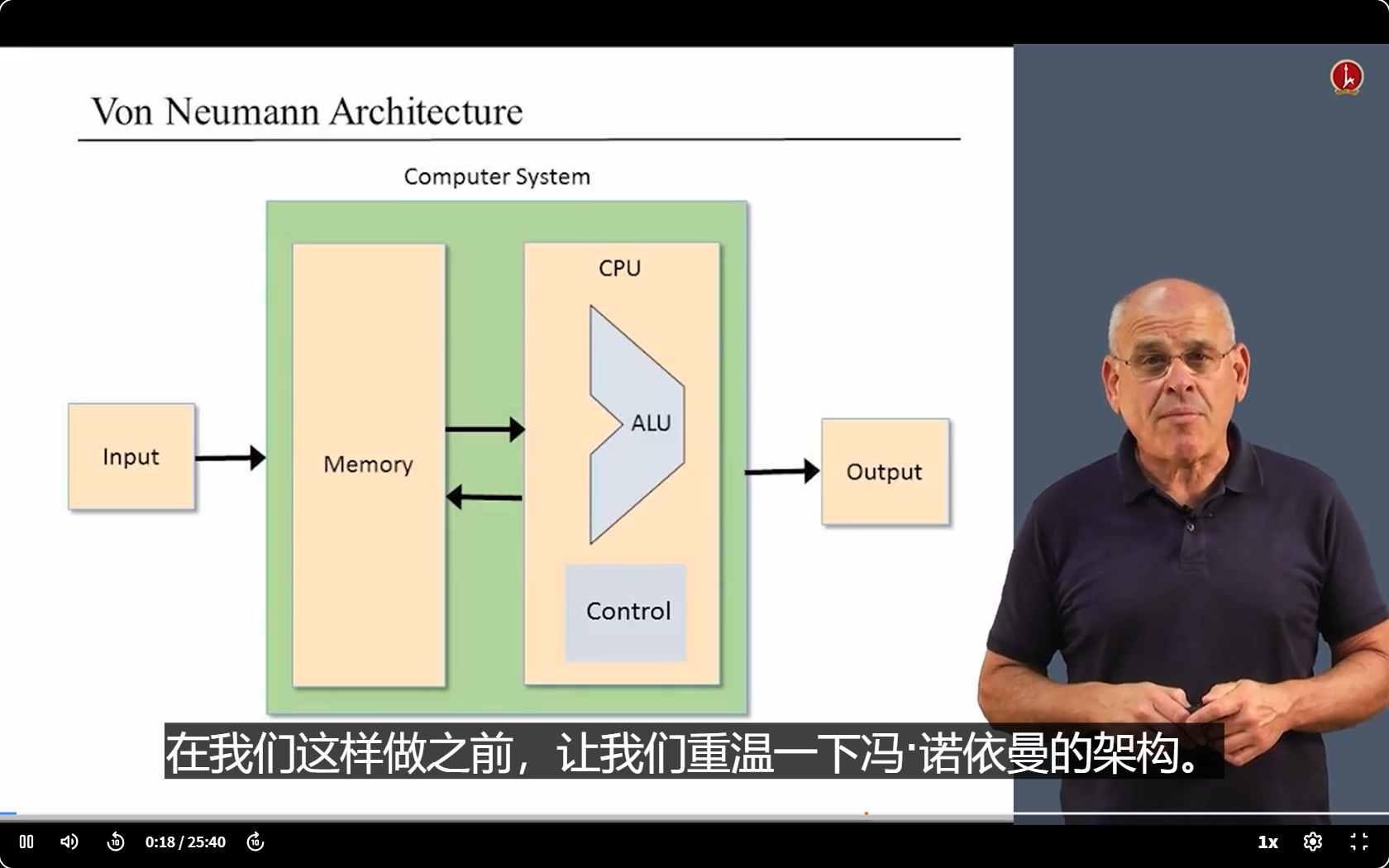

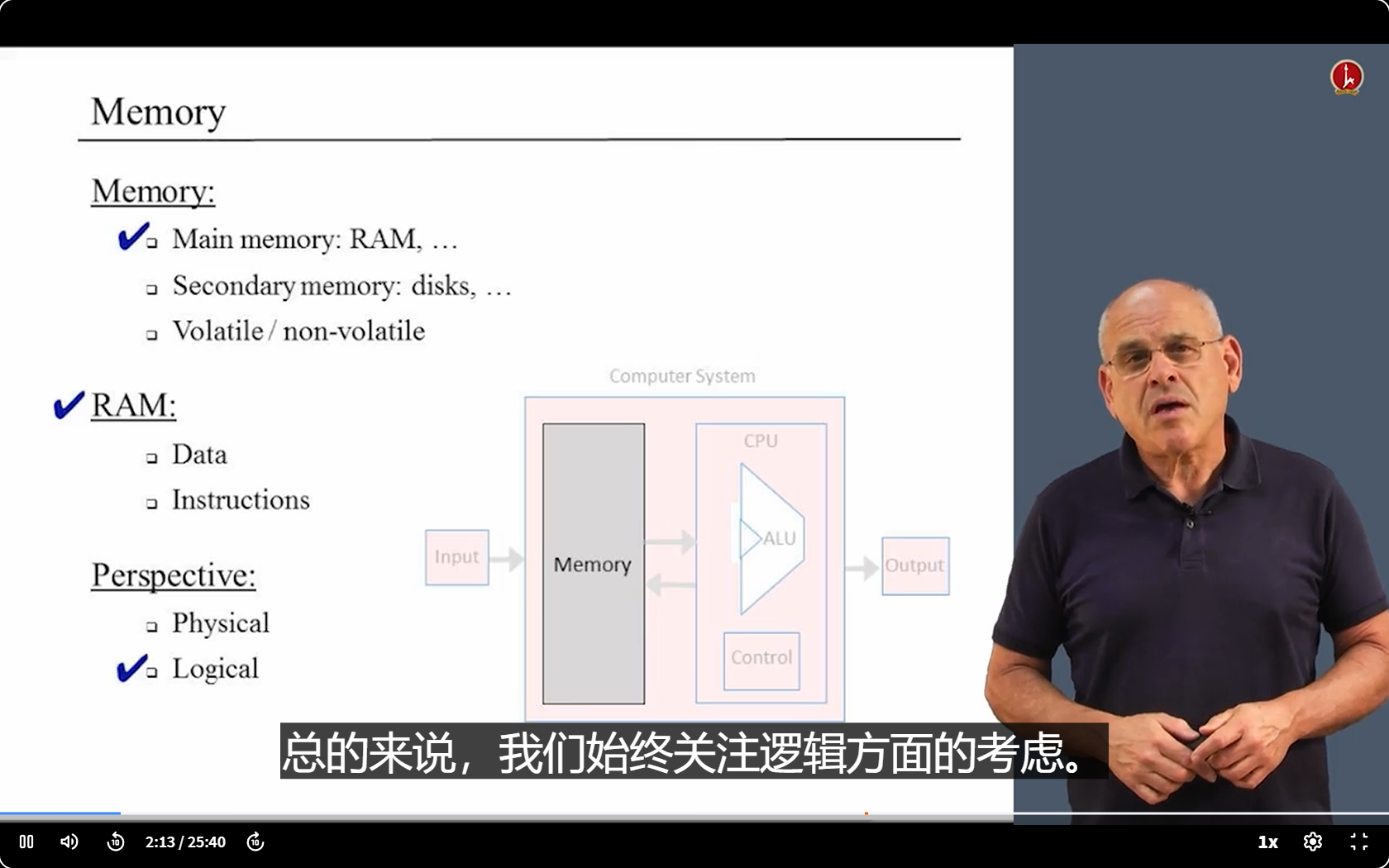

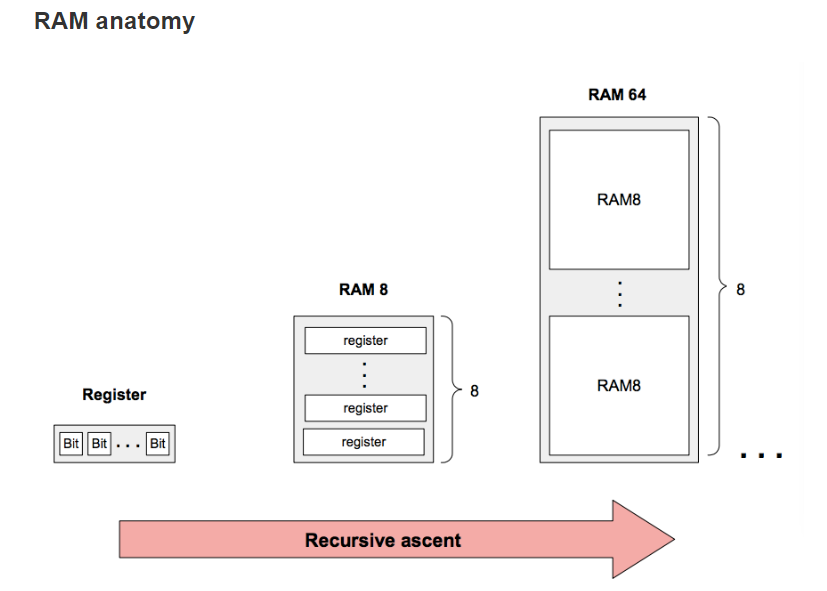

3.3 Memory Units

Memory

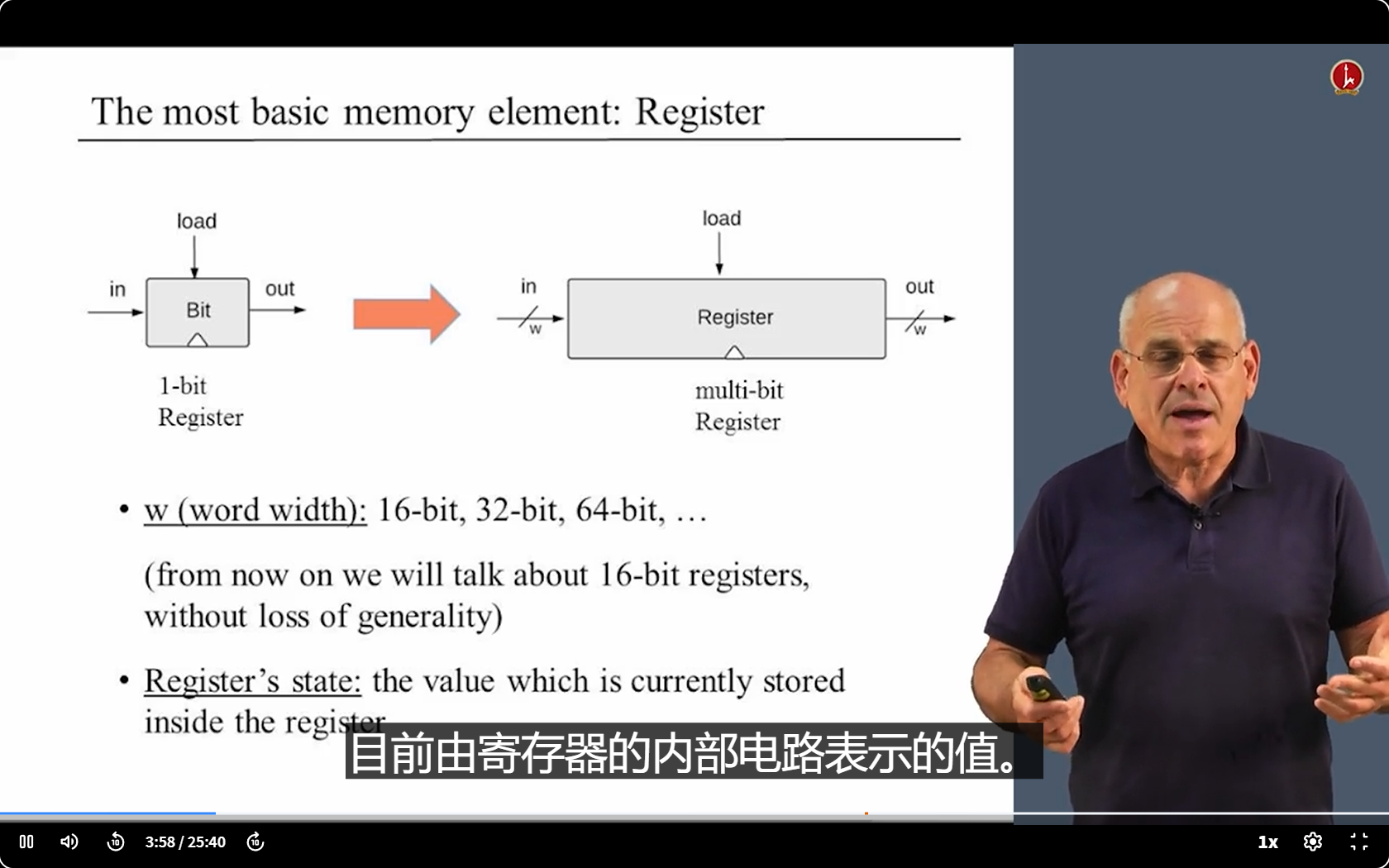

The most basic memory element: Register

⭐ (并着排列的)

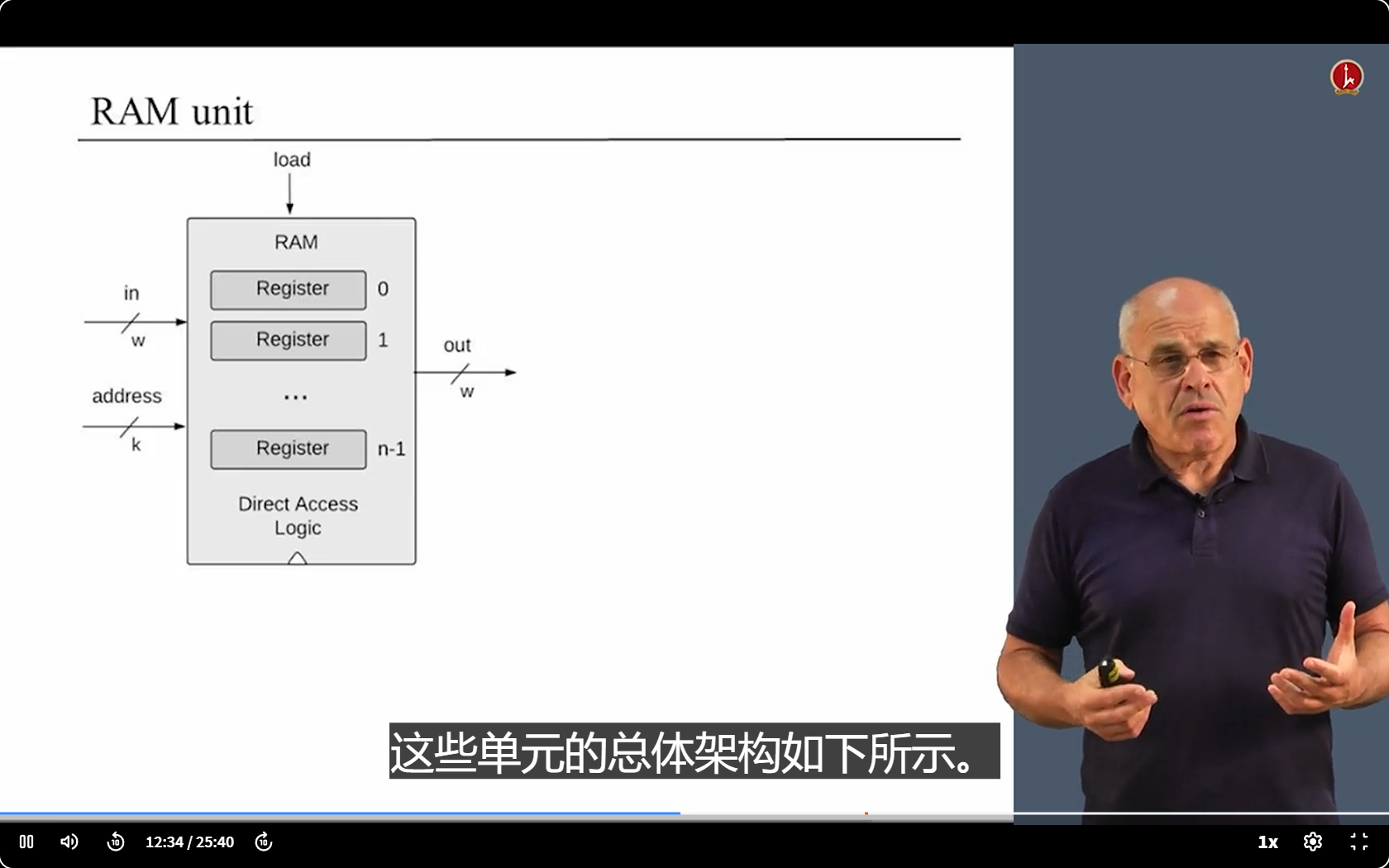

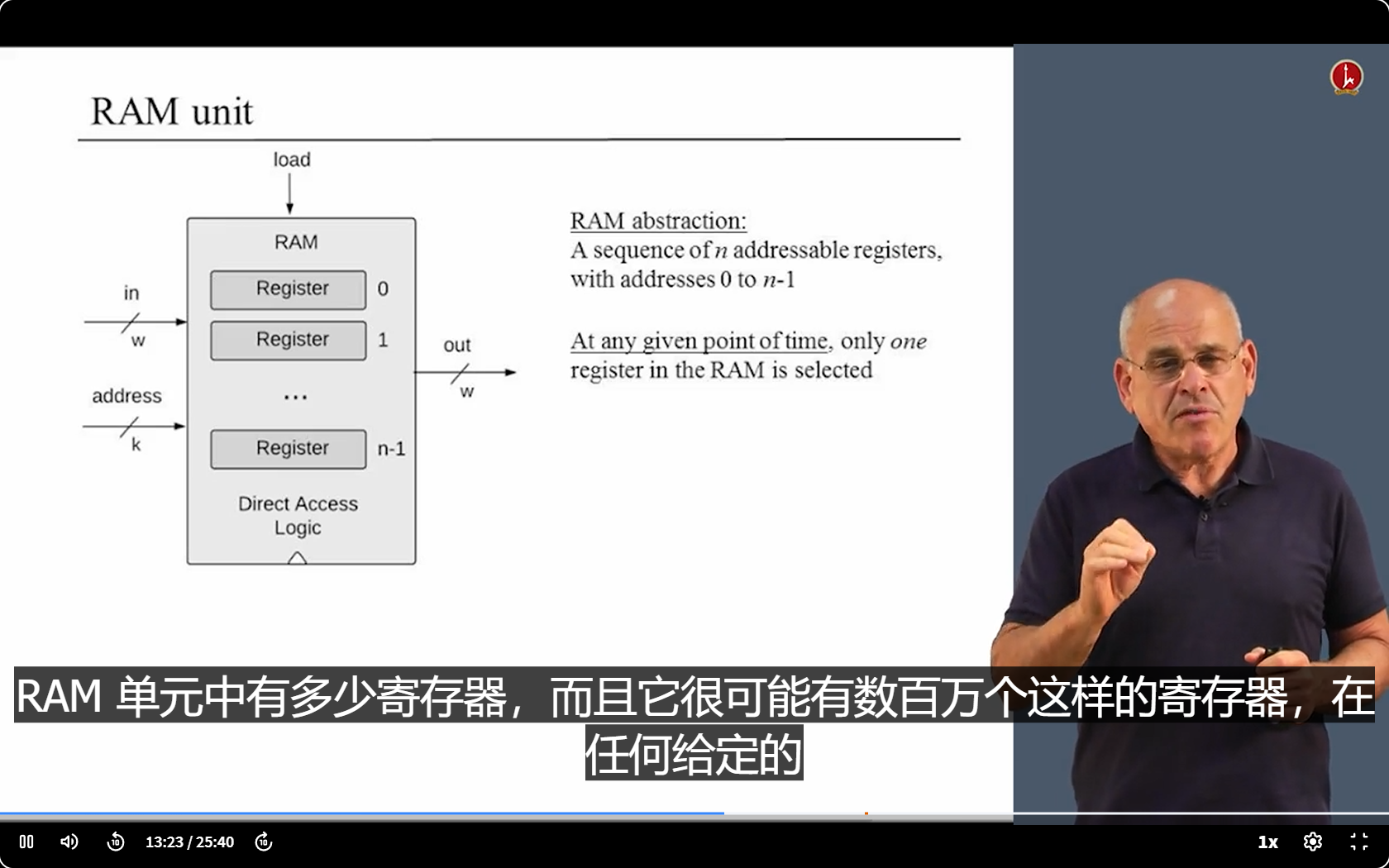

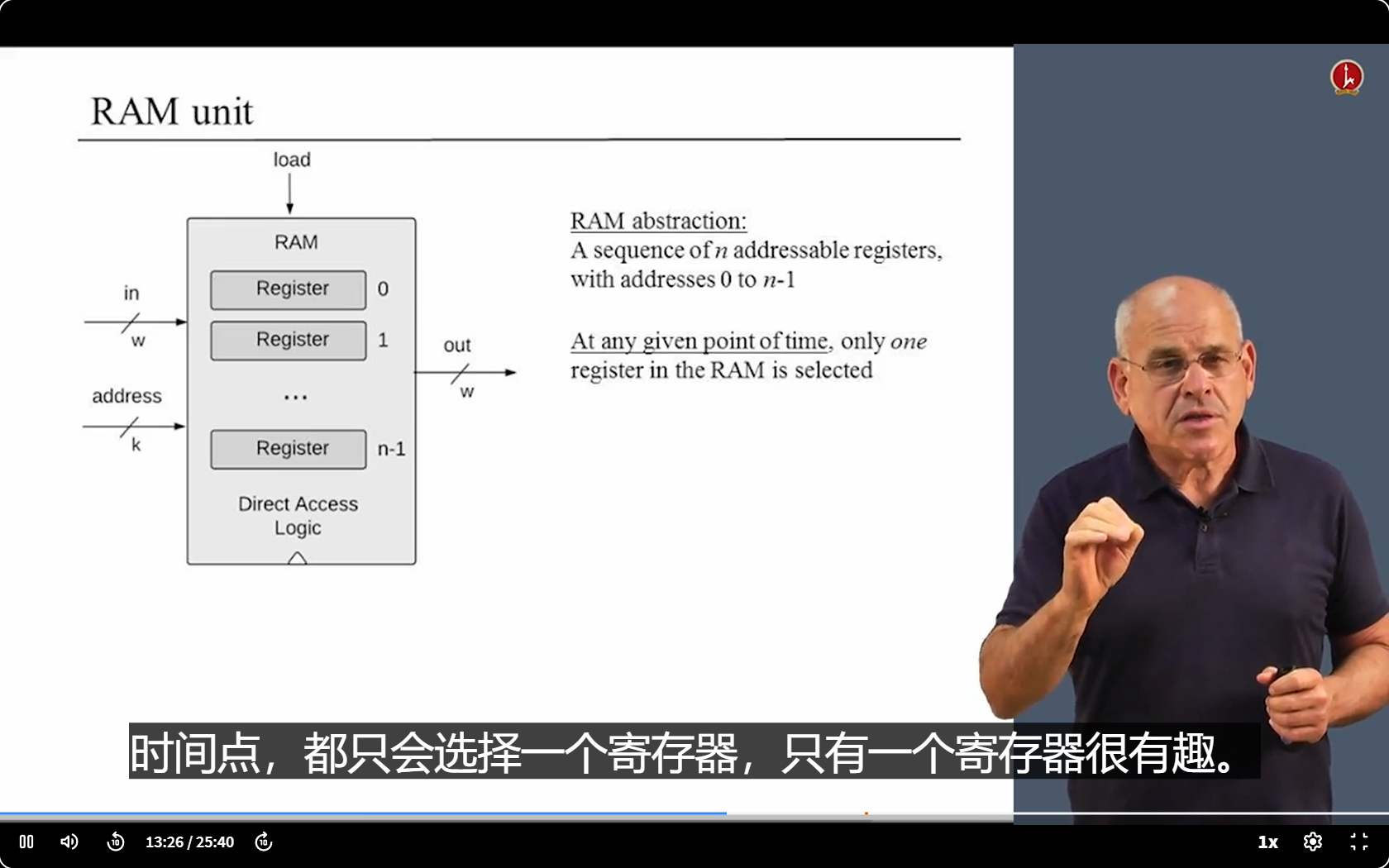

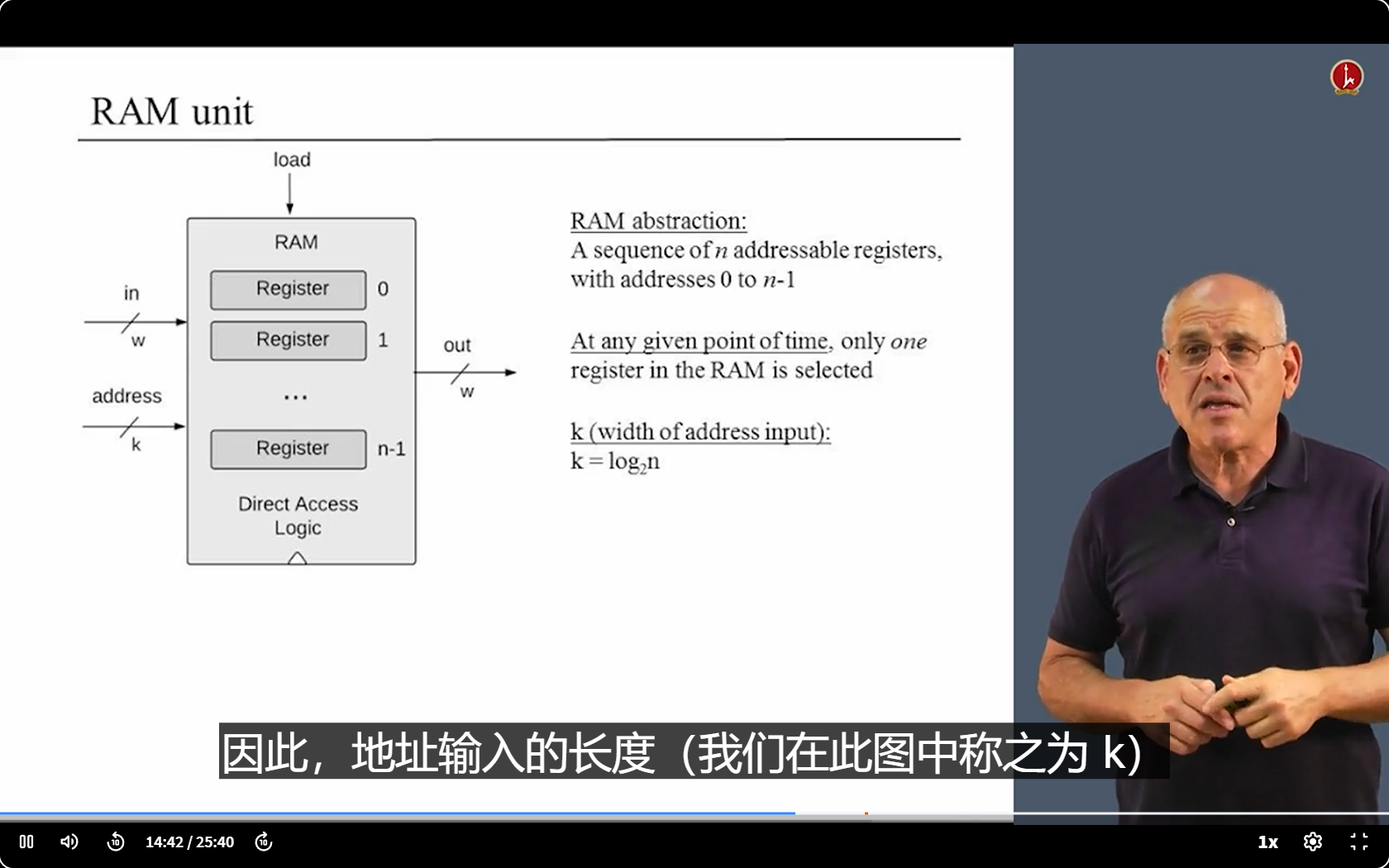

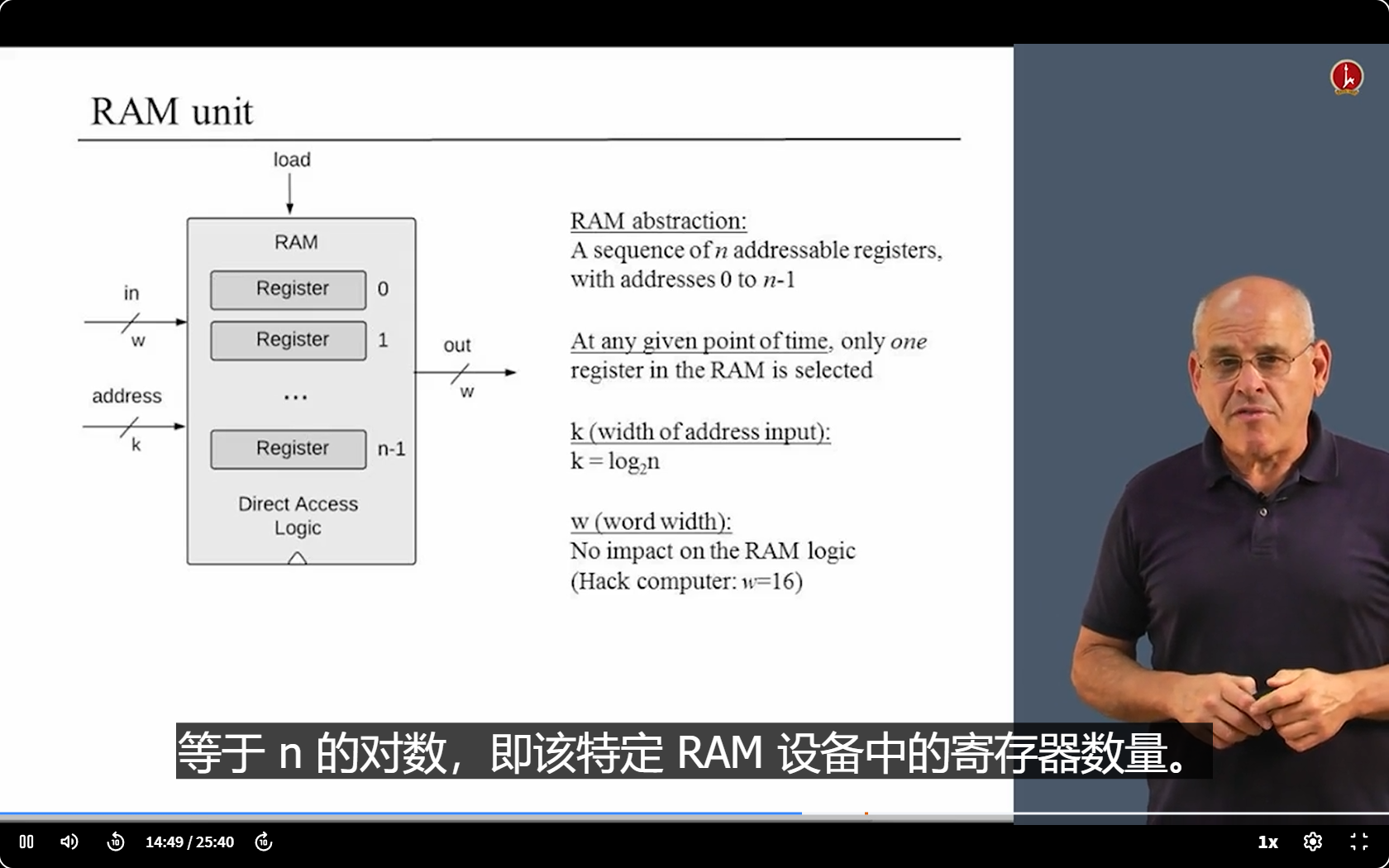

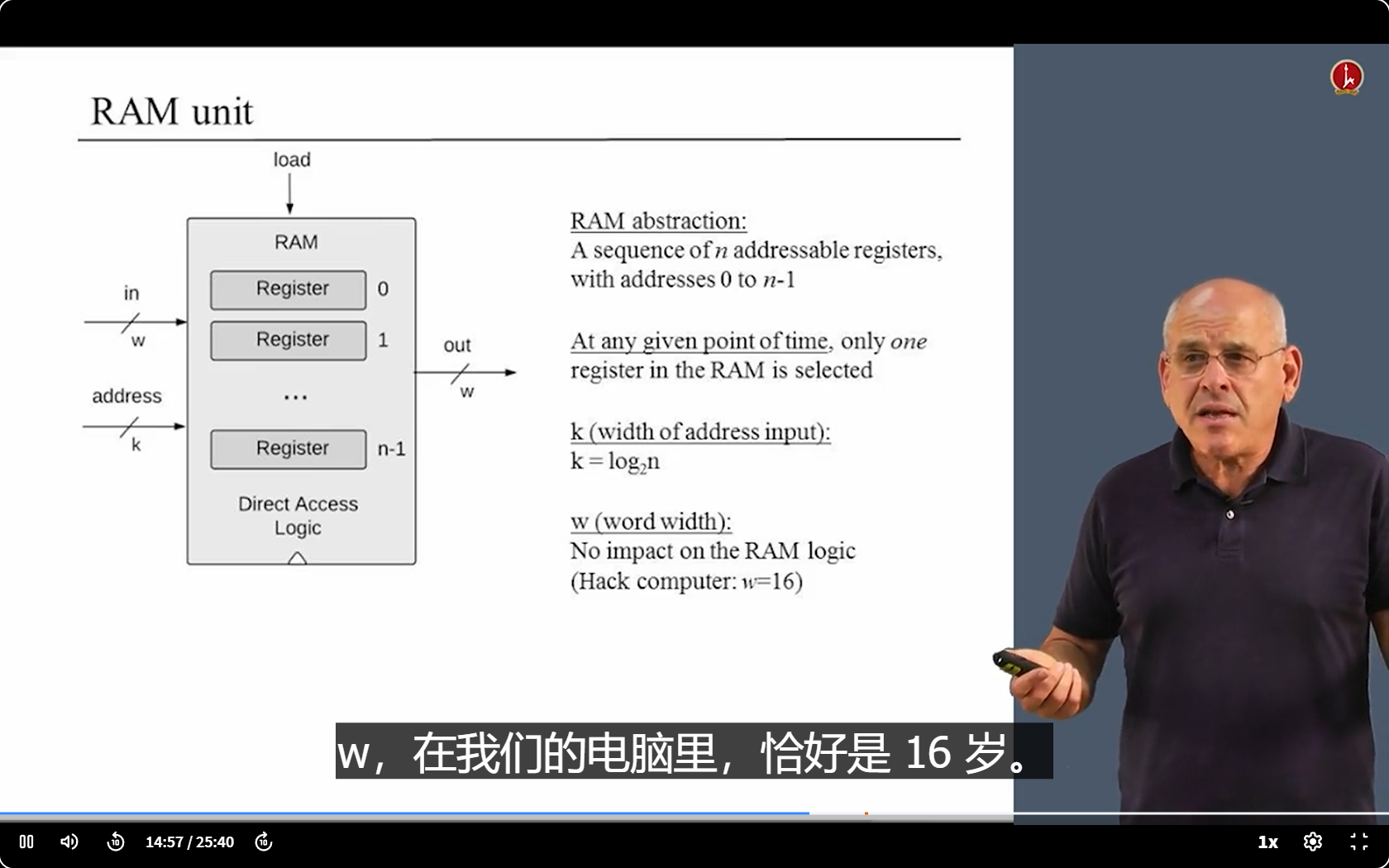

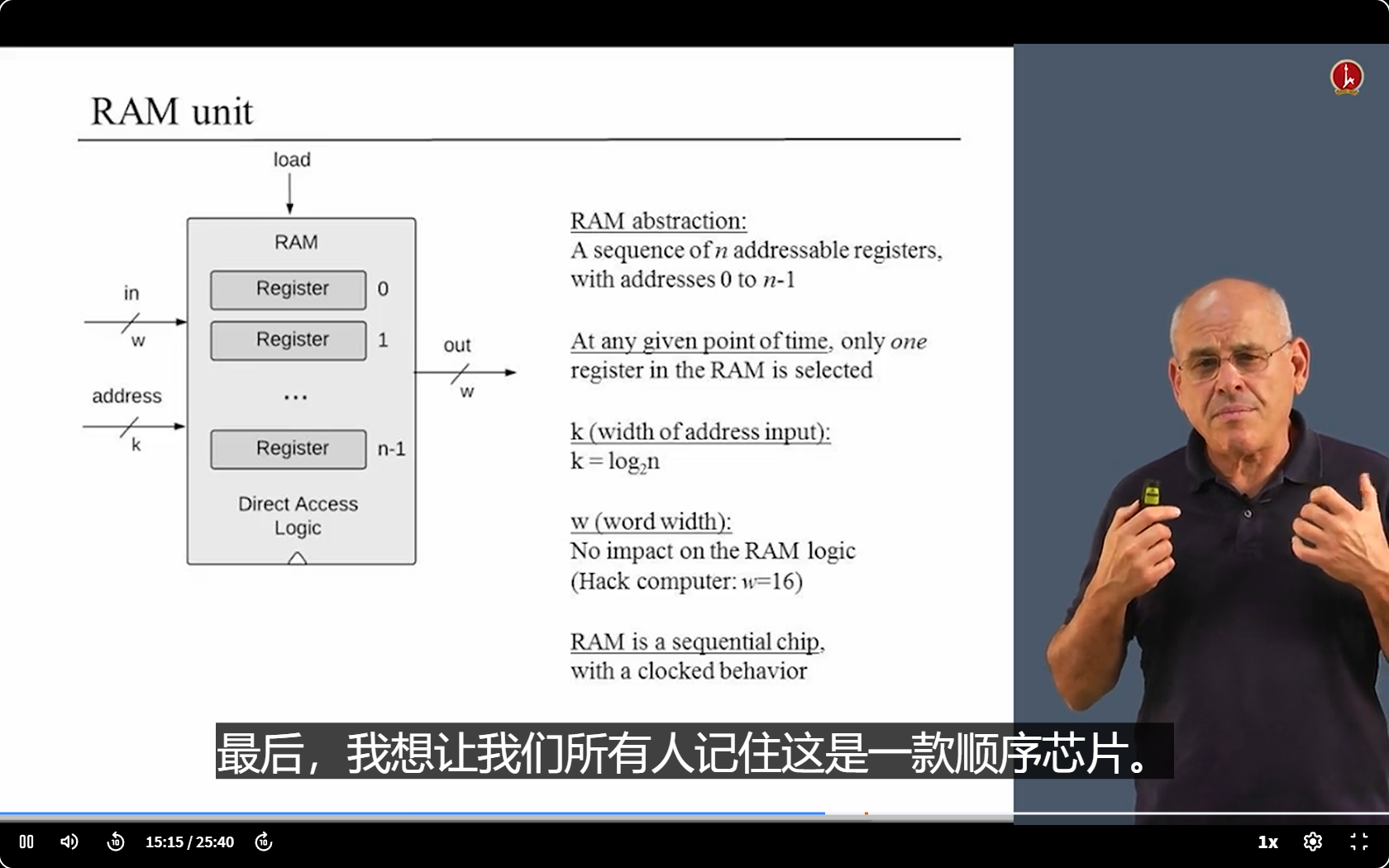

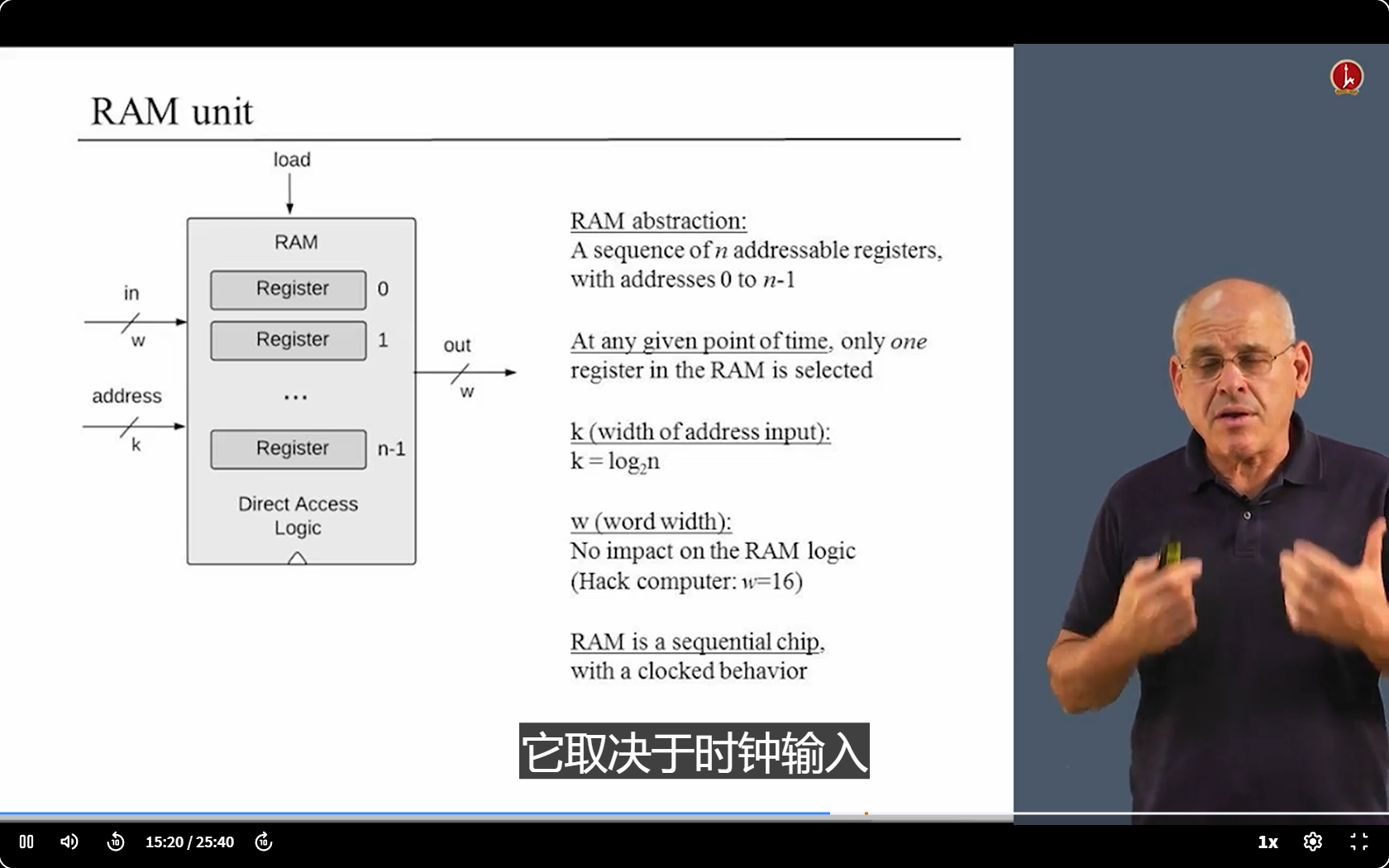

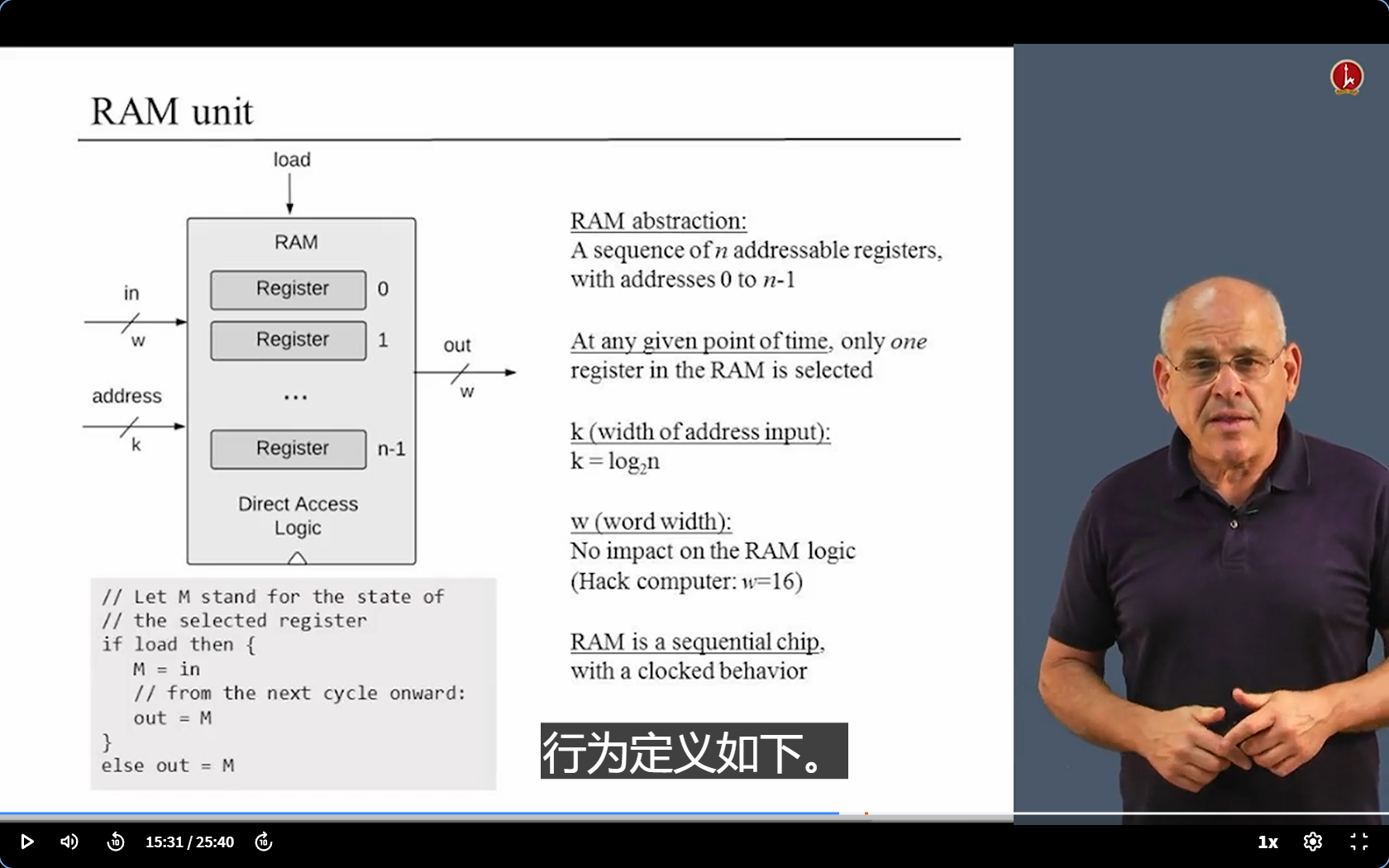

RAM unit

(逻辑时序的芯片)

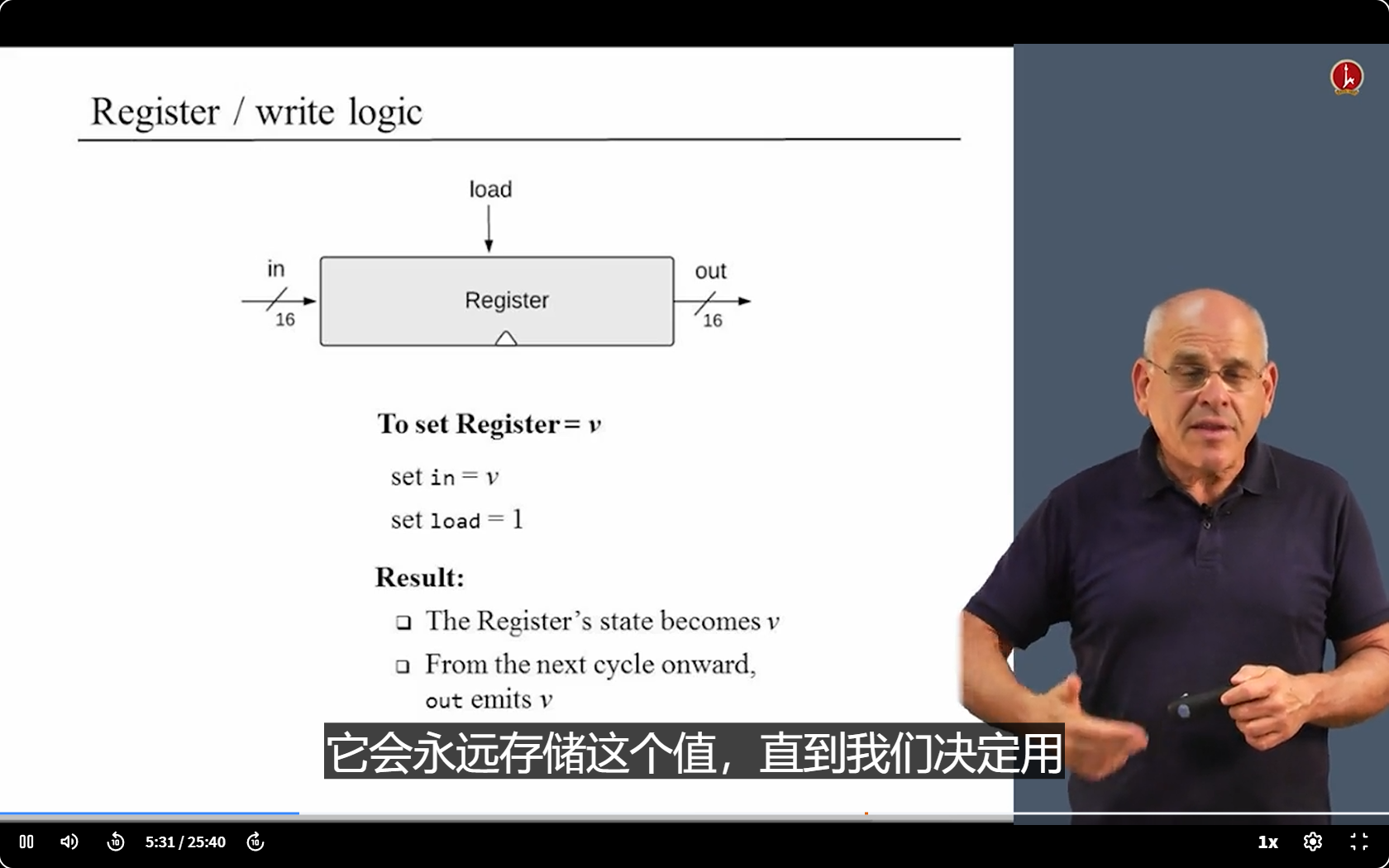

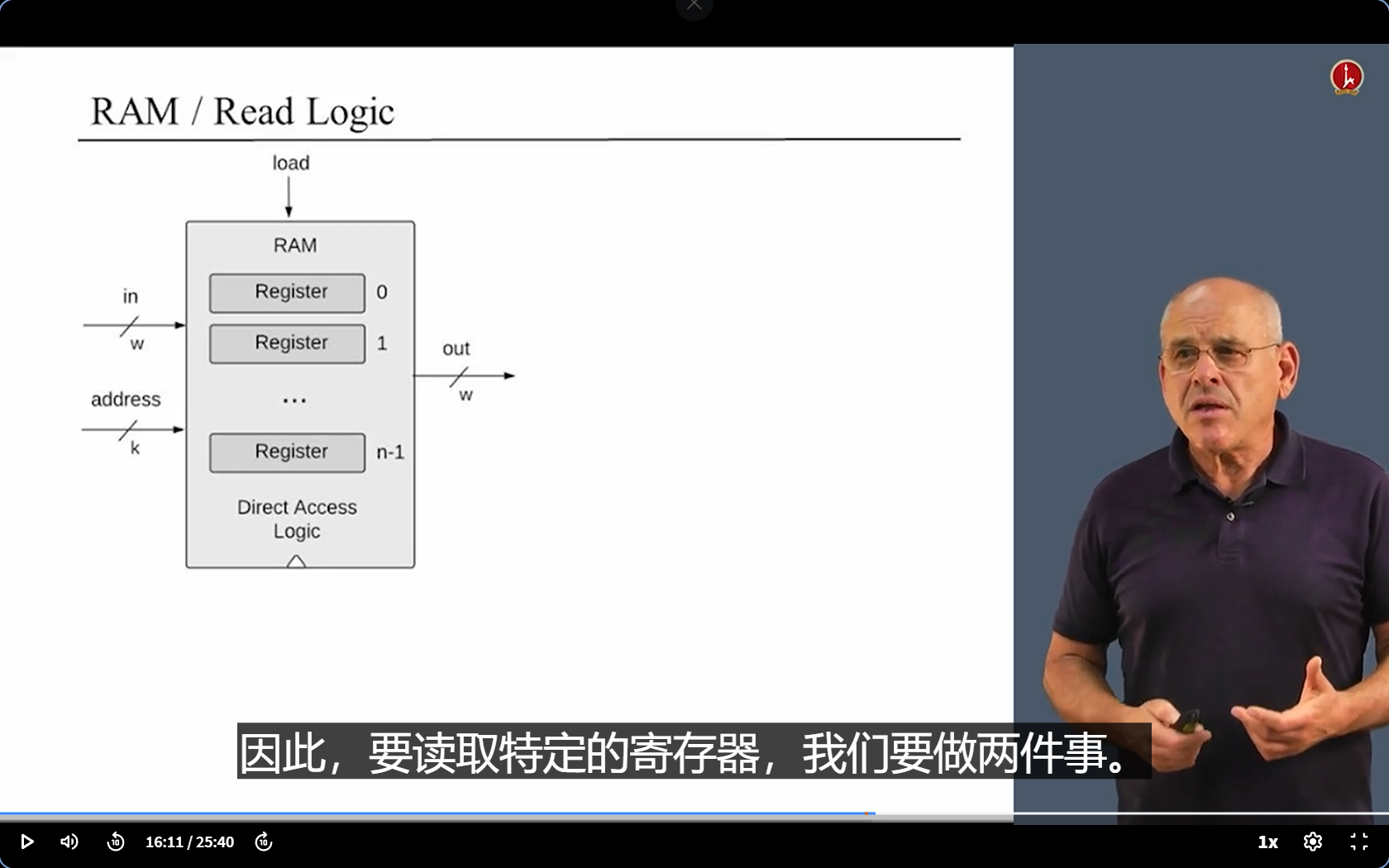

RAM / Read Logic

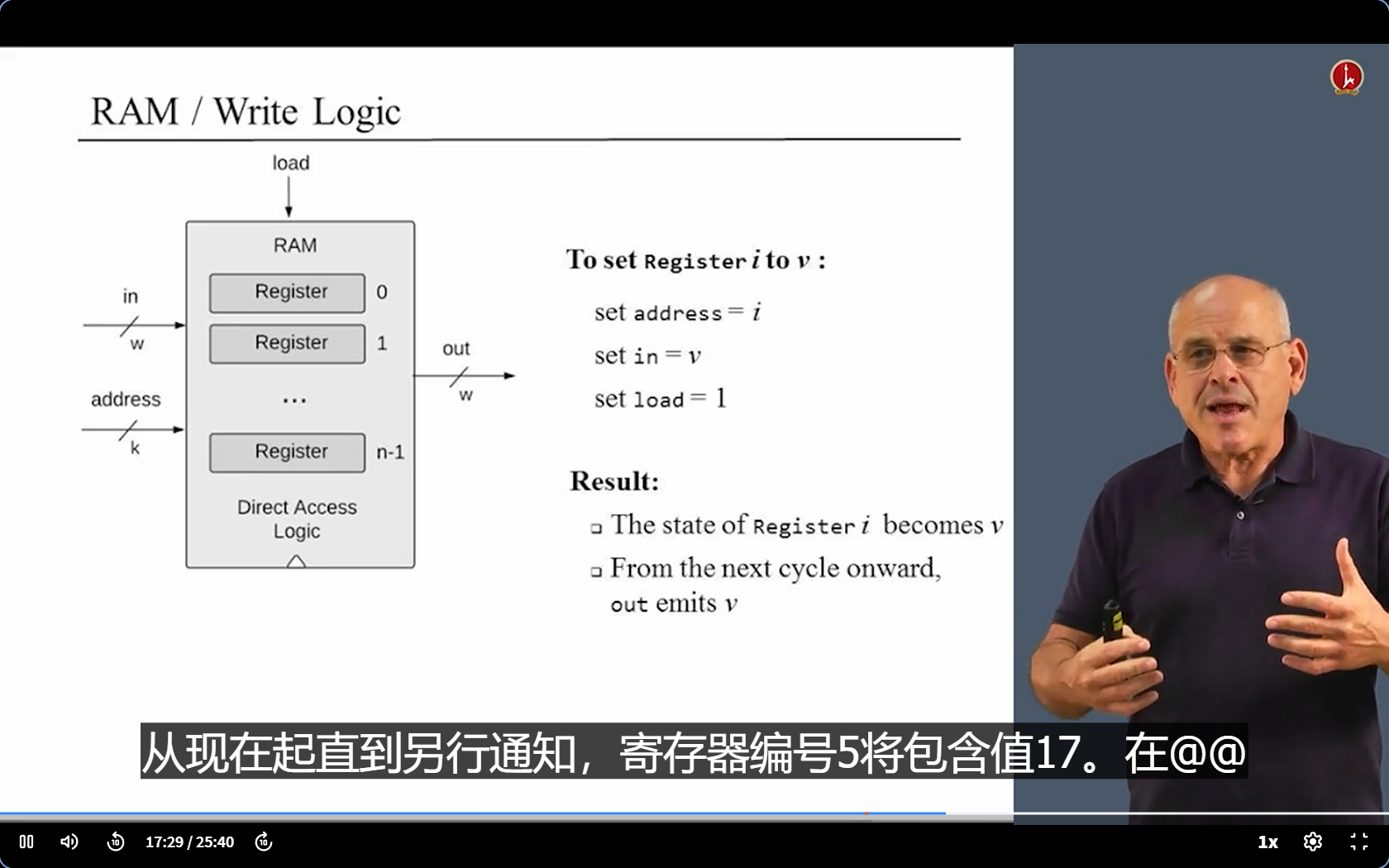

RAM / Write Logic

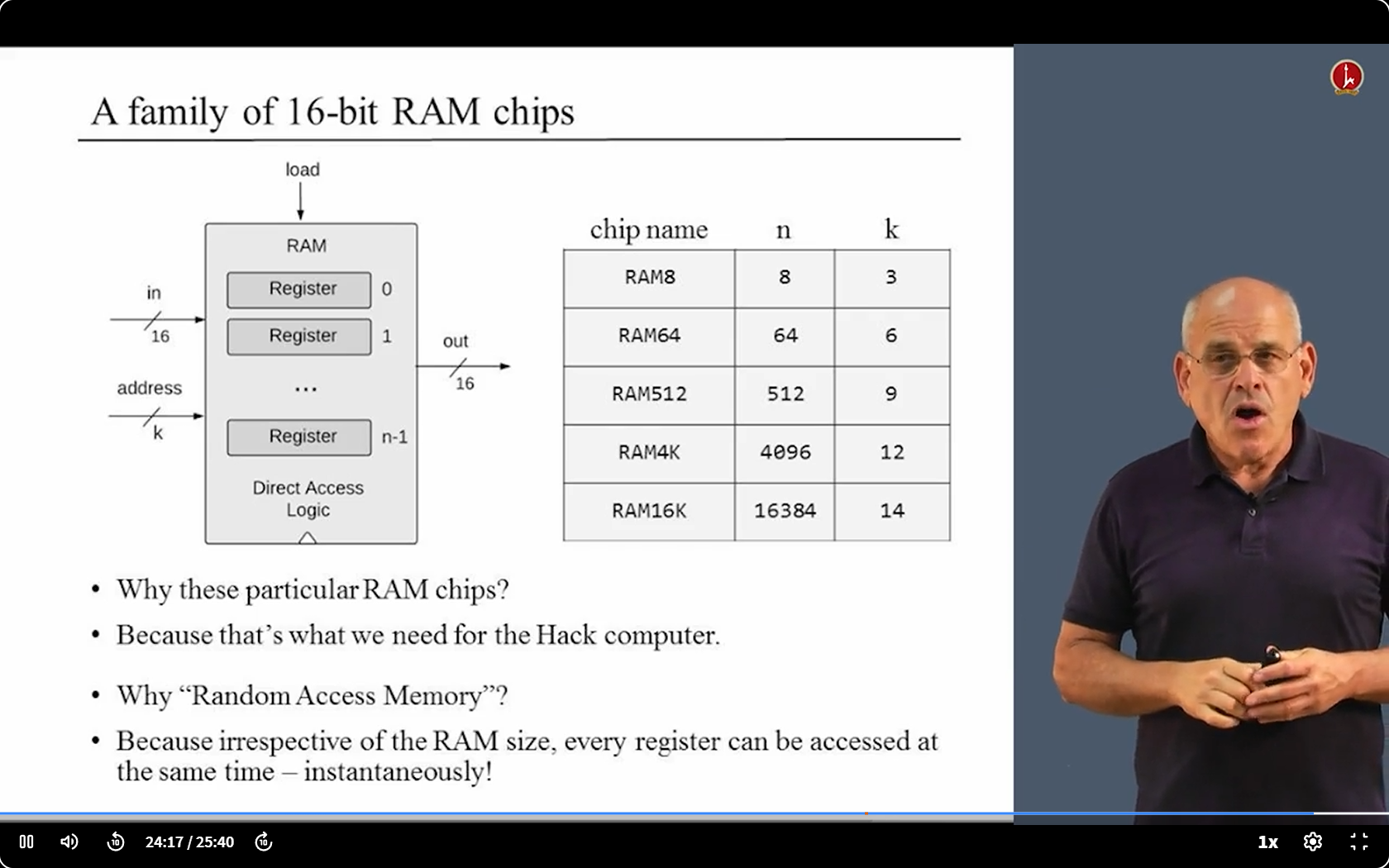

A family of 16-bit RAM chips

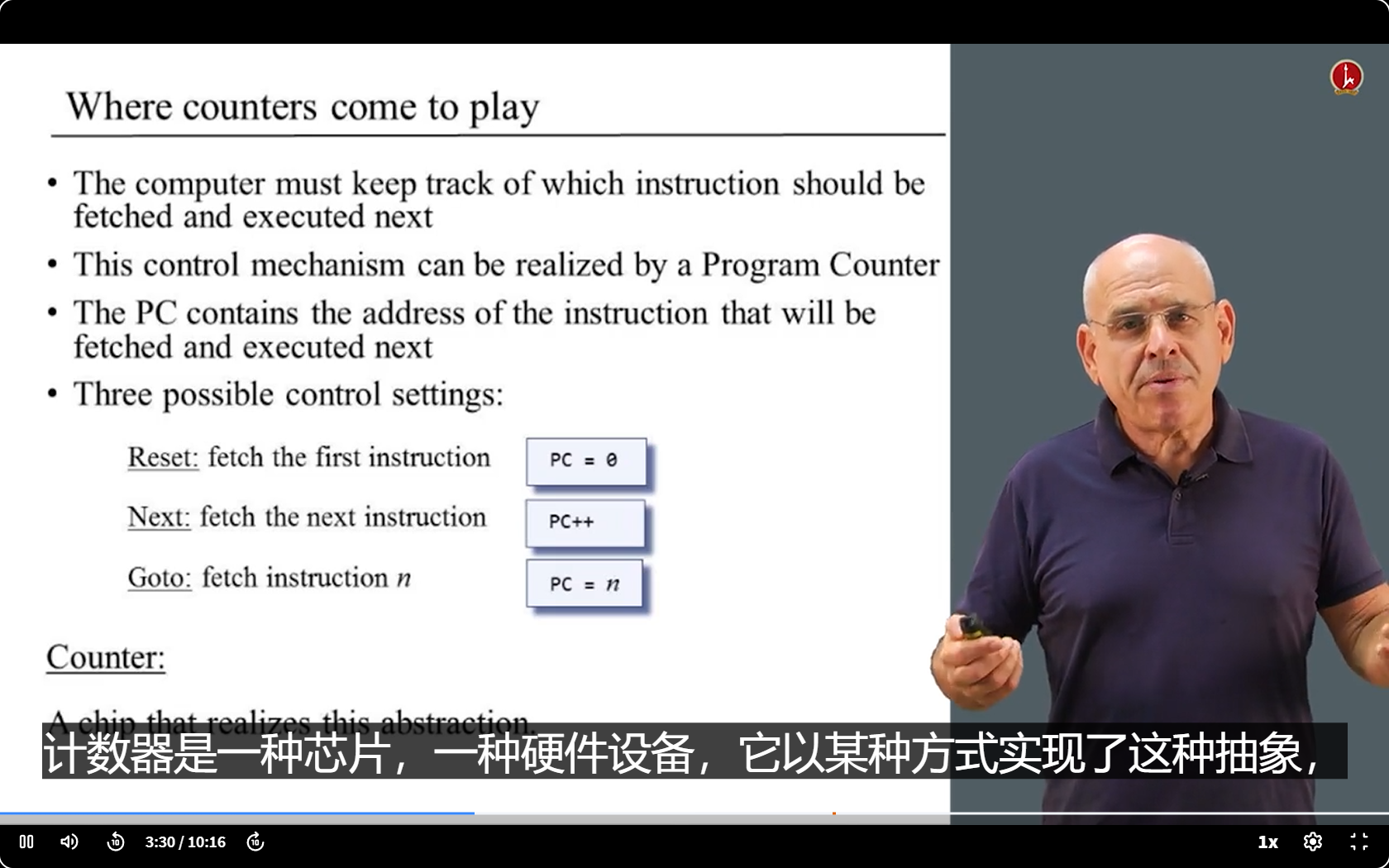

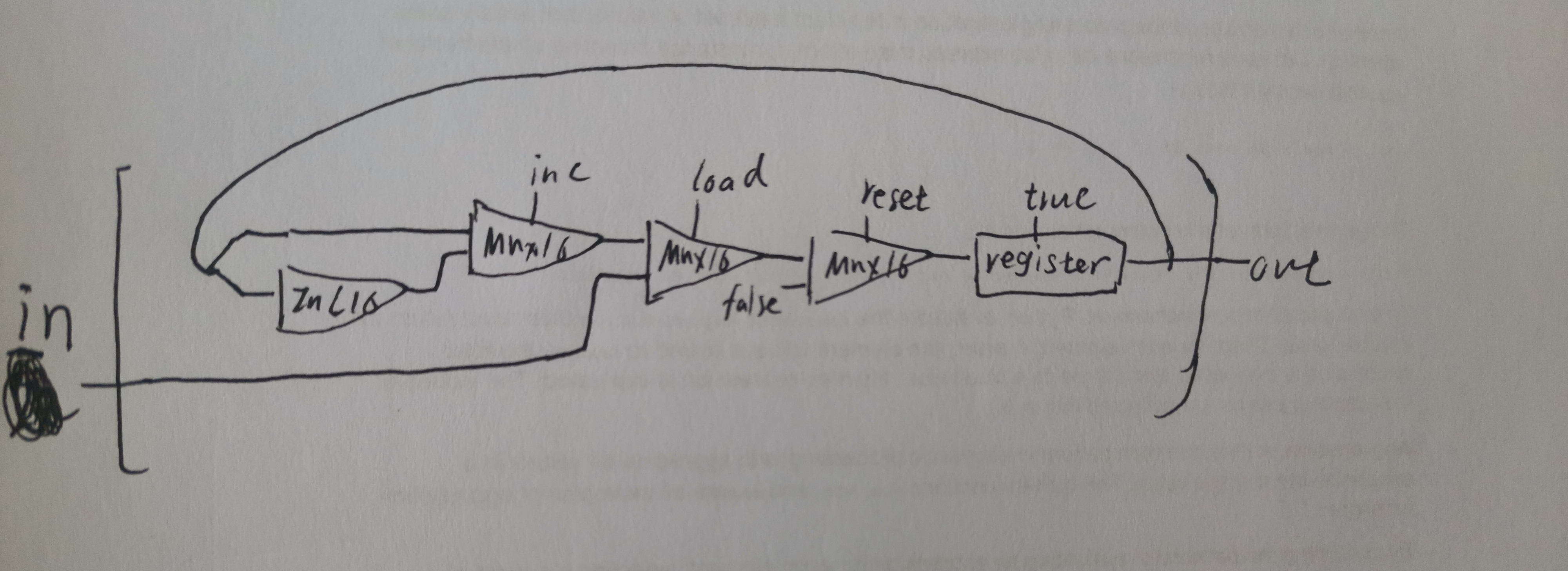

3.4 Counters

(Inc 代表增量[+1])

3.5 code

preview:DFF

1-bit register 芯片

- 输入一个1-bit的数。如果load=1,下一秒输入该数,如果load=0,下一秒保持原来的数值。

- register 中文:寄存器

1 | CHIP Bit { |

16-bit register 芯片

- 输入一个16-bit的数。根据load,下一秒输出该数,或者下一秒保持上一秒的值。

- 1个load决定16个输出。16个1-bit register芯片并排。

- 对每一位进行load运算

- 最终的输入/输出 都是 一个 16-bit的数

.jpg)

.jpg)

1 | // 16-bit 寄存器! |

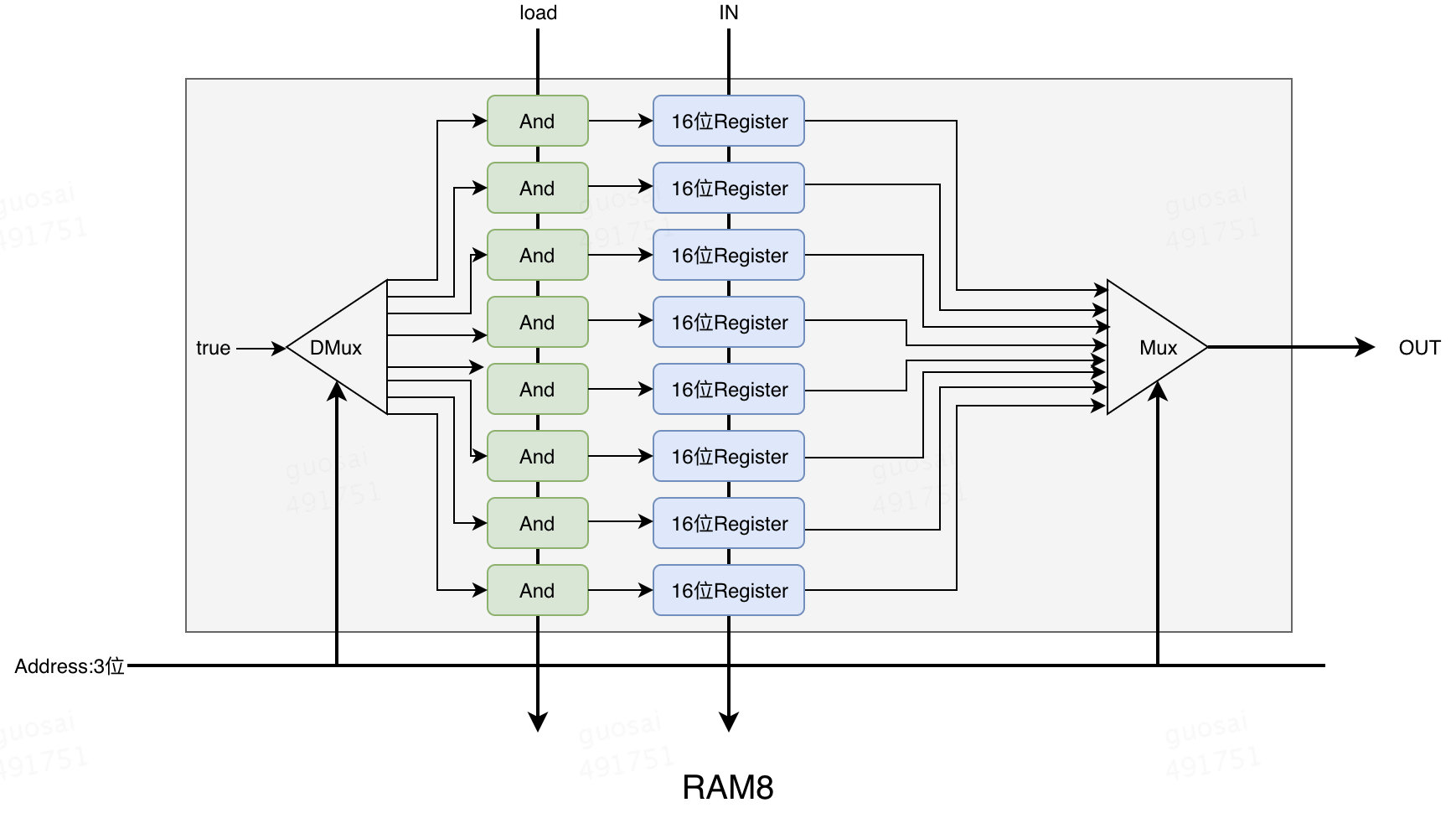

RAM8

- 8个 16-bit寄存器,并排放在RAM8里。

- 输入:一个16-bit 的数。输出为 一个 16-bit 的数 (数最大 16-bit,可小点)

- ⭐根据三位数地址address决定给 哪一个 register储存值。

- 对应的被调到的寄存器的load会被打开,load=1。

1 | CHIP RAM8 { |

RAM64

- 原理同RAM8:一个最大16-bit的输入,根据address(解码后)决定把改 一位数值 保存在哪个地方(该地方的load会打开)

- (结构由 8个RAM8 并排拼一起,解码端口变多了点,当然了address也长了点)

1 | CHIP RAM64 { |

RAM512

- 原理同上,就是积木从小拼到大(8个RAM64)

1 | CHIP RAM512 { |

RAM4K

- 8个RAM512

1 | CHIP RAM4K { |

RAM16K

- 4个RAM4K

1 | CHIP RAM16K { |

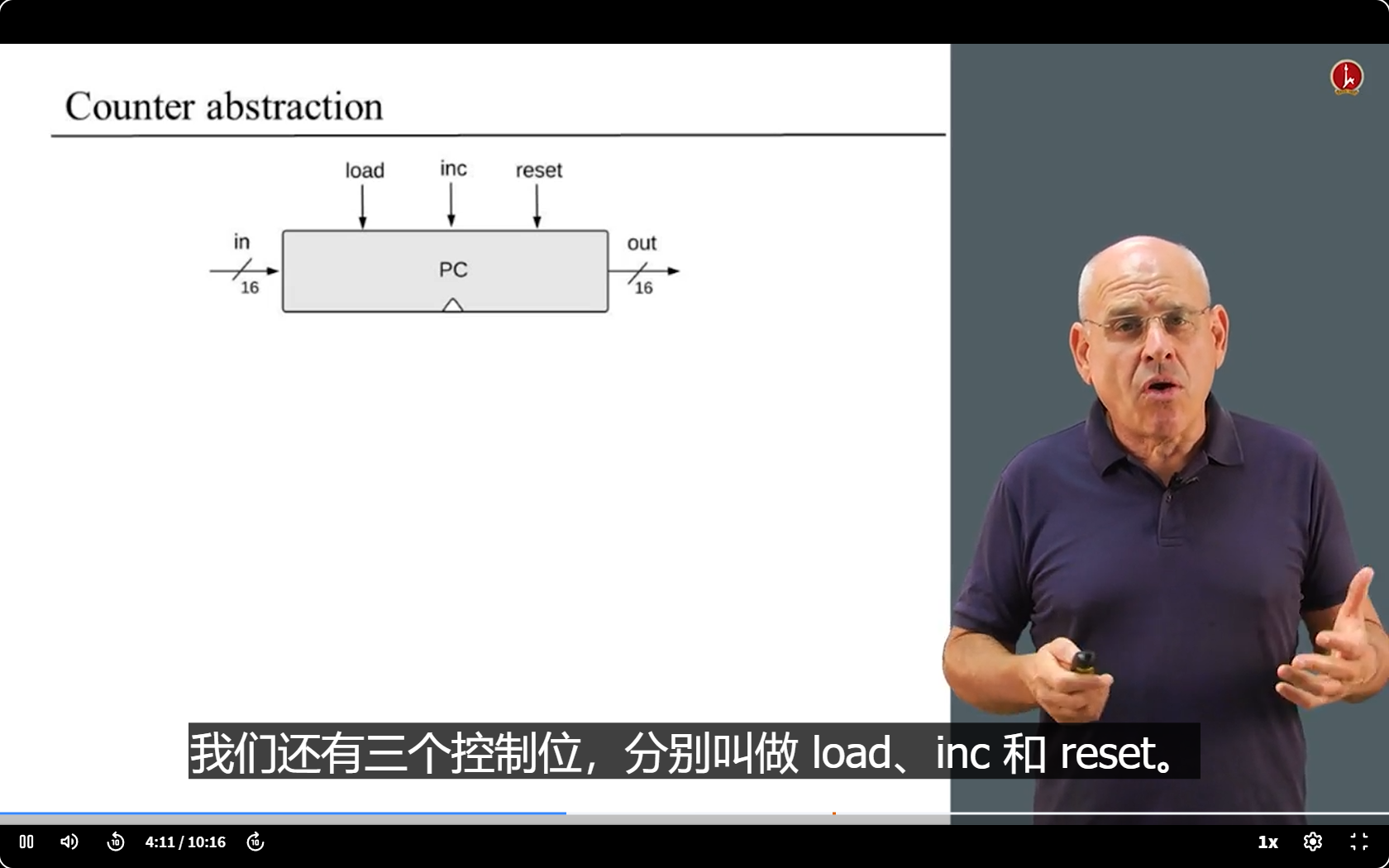

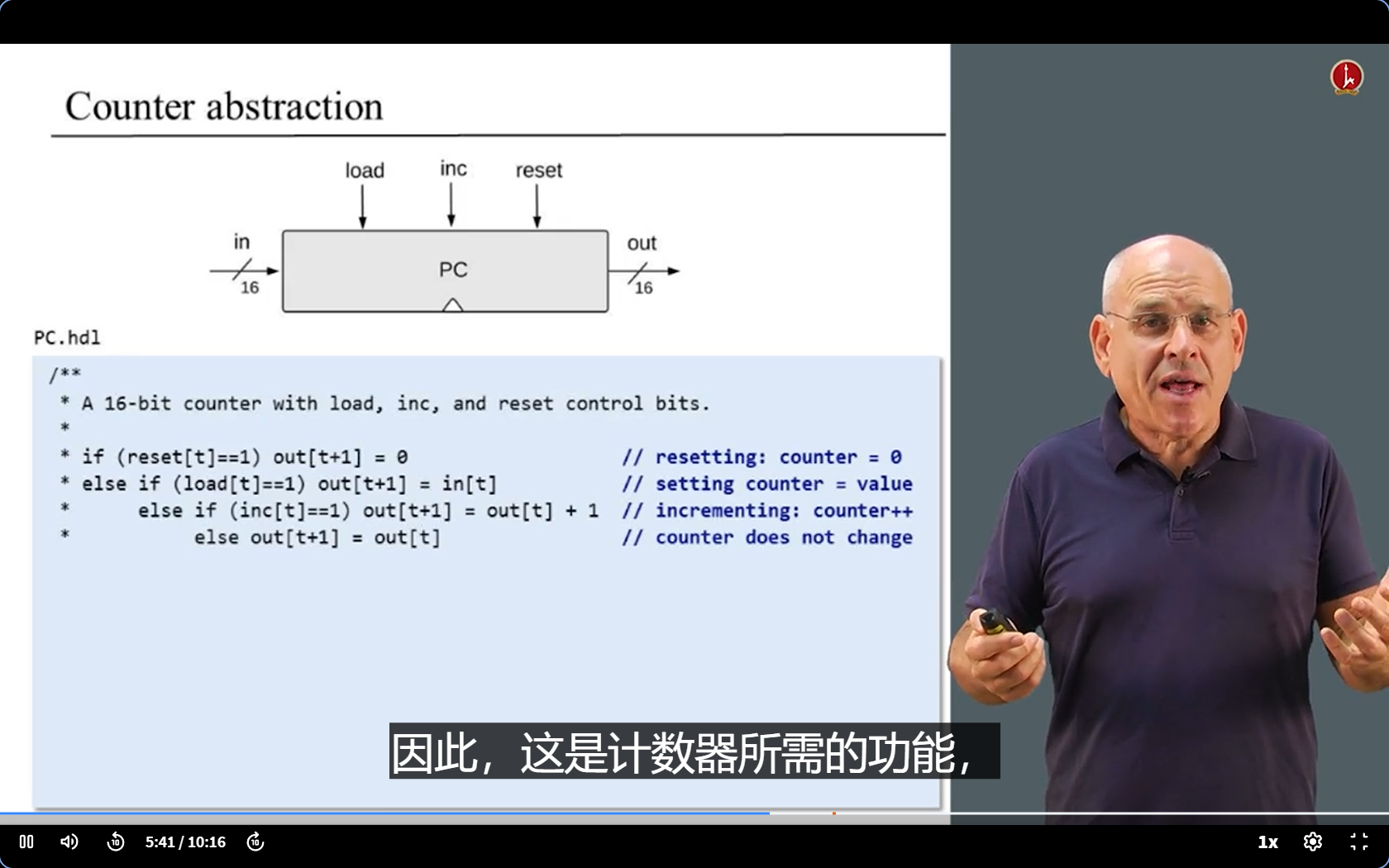

CHIP PC

1 | /** |

评论