计组-7.3 I/O控制方式

7.3 I/O控制方式详解

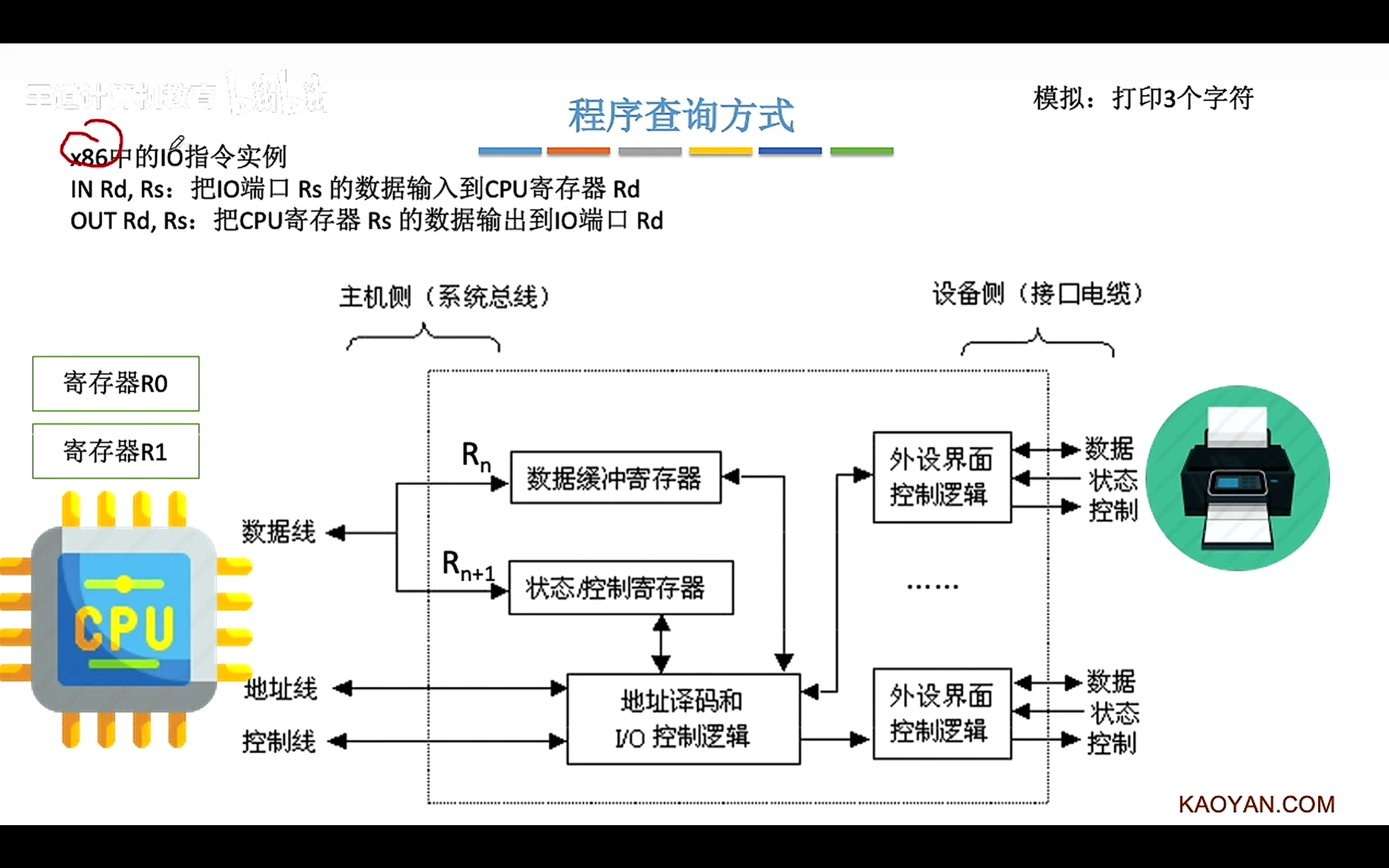

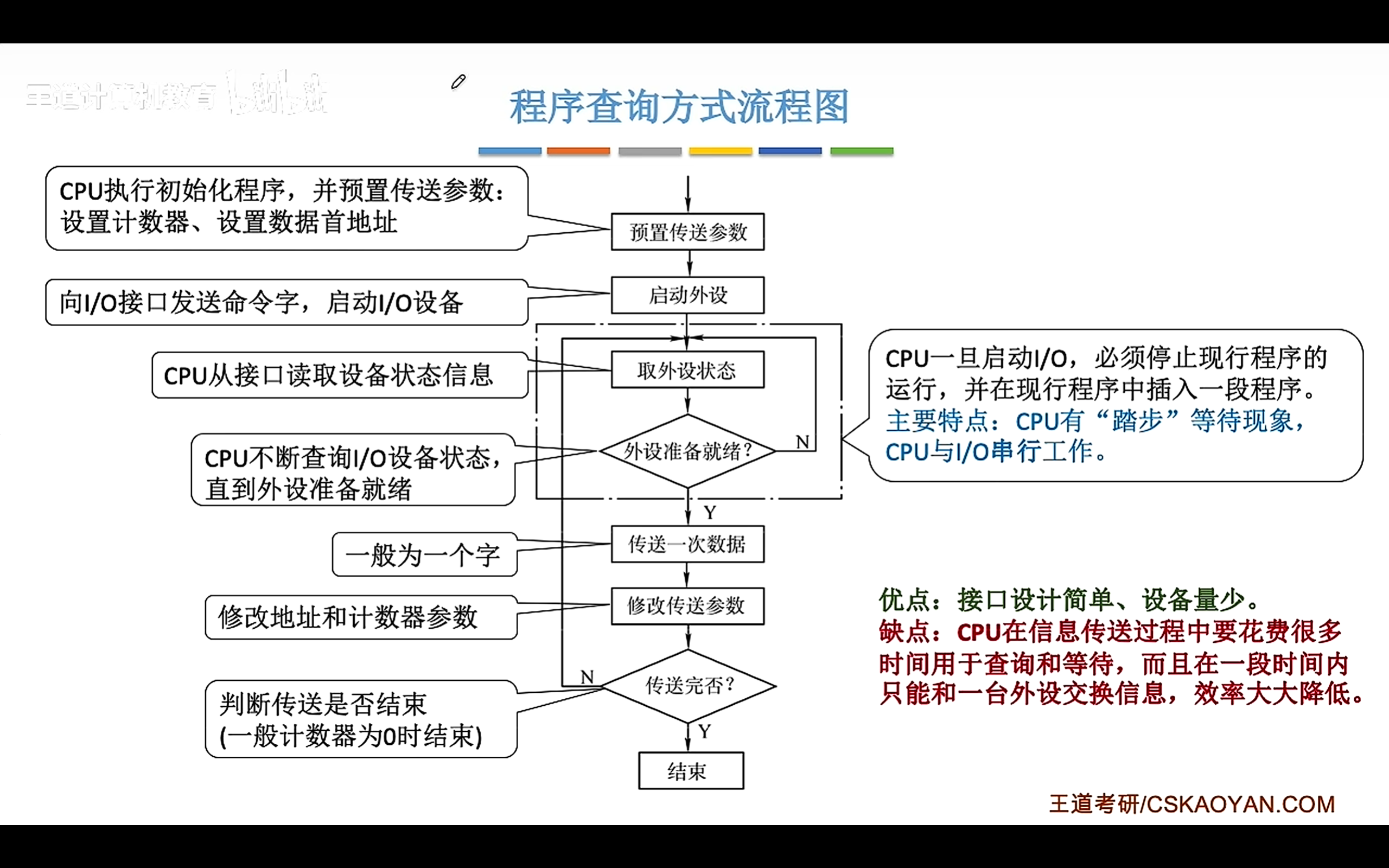

程序查询方式

工作流程

①CPU读取状态寄存器是否busy。

不 busy 后,CPU发送(要打印的)数据到数据缓冲寄存器。

打印机开始工作,同时把状态寄存器设置为busy。

CPU速度比打印机快很多,打印机工作的时候,计算机发送询问,重复第①步

- 程序查询方式有两种:独占查询。定时查询。

打印机完成后,发送ready信号,busy位清零。

CPU可以打印 下一个 数据。

所有数据打印完成后,CPU向I/O接口的控制寄存器发送结束命令。

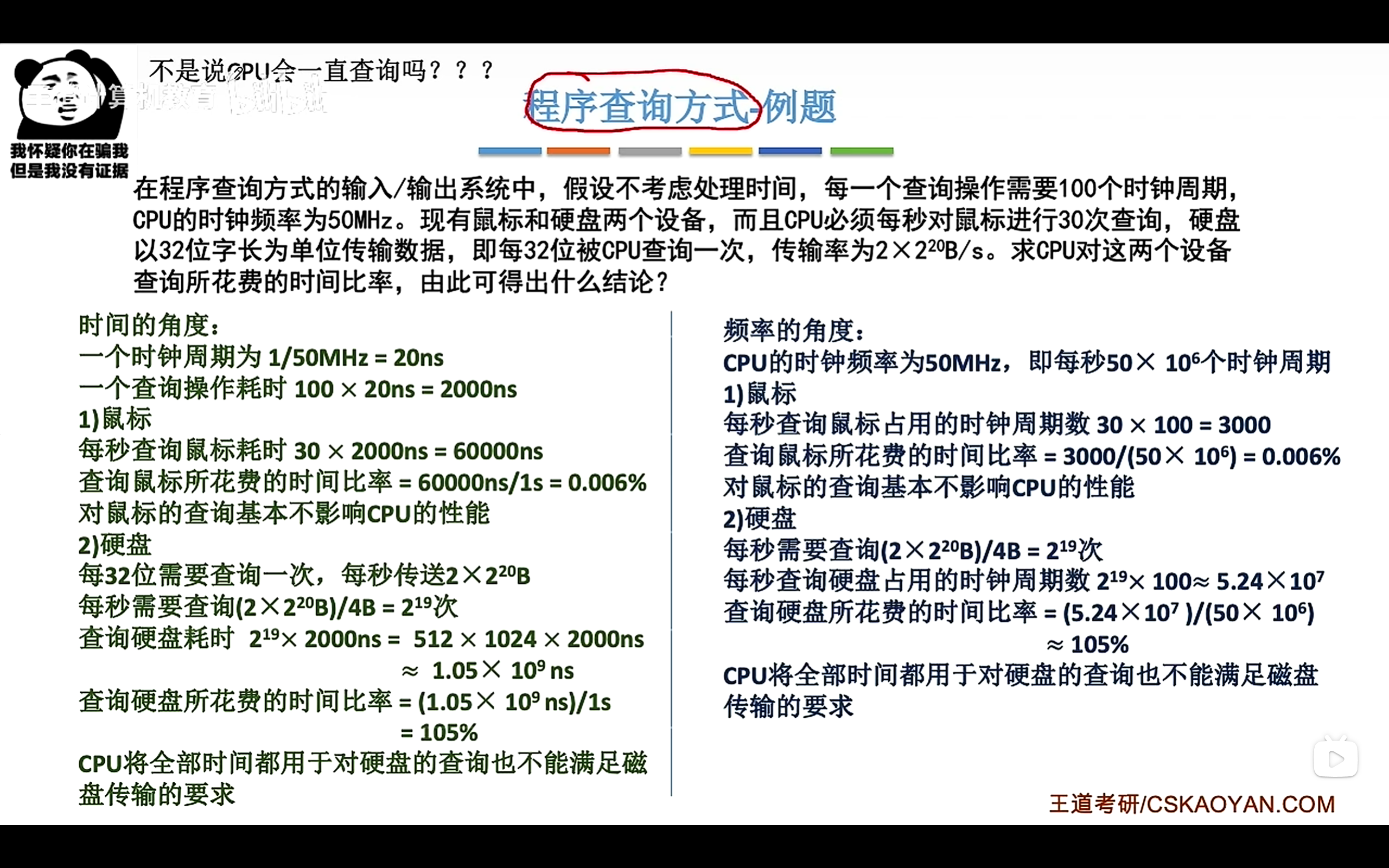

例题

从例题中可以看出,程序查询方式对慢速设备没影响,但是对于查询次数多的设备不支持。所以需要别的IO交互方式才行。

特点:CPU原地踏步。

优点:接口设计简单,设备量少。

缺点:费时。

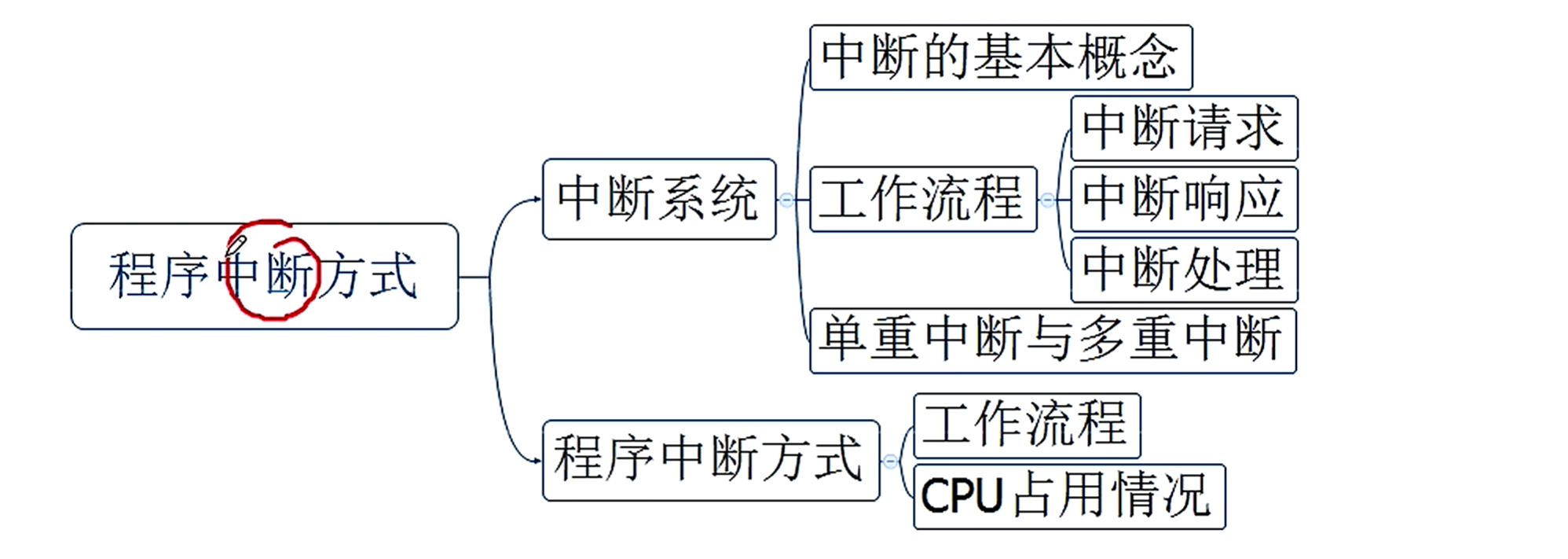

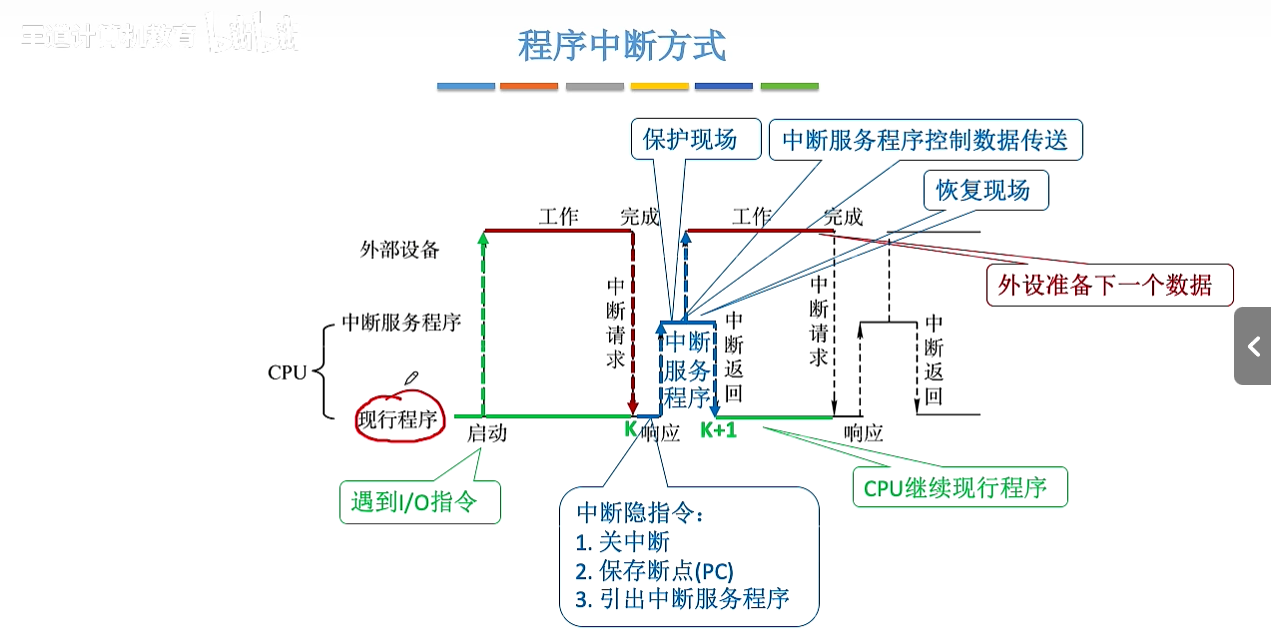

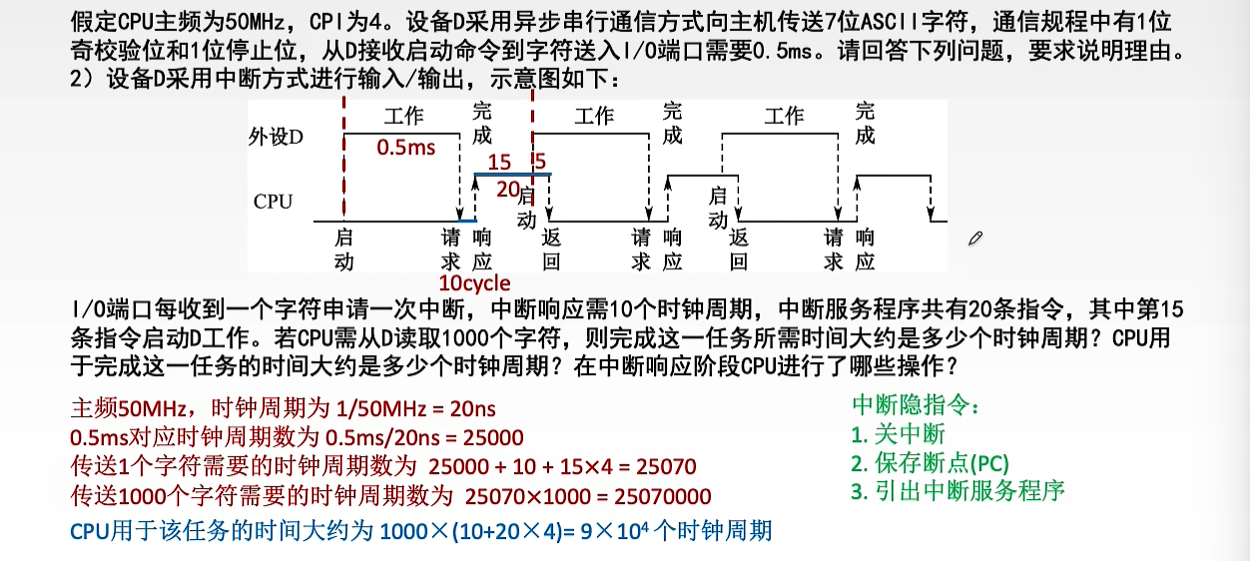

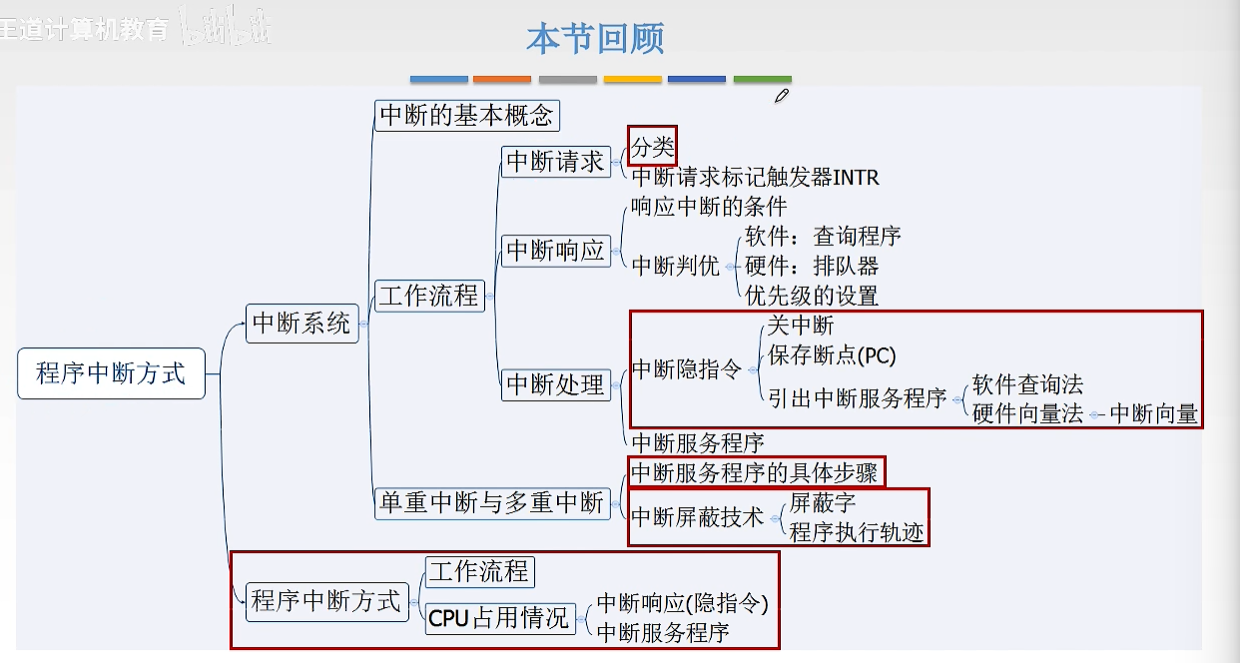

程序中断方式

==工作流程==

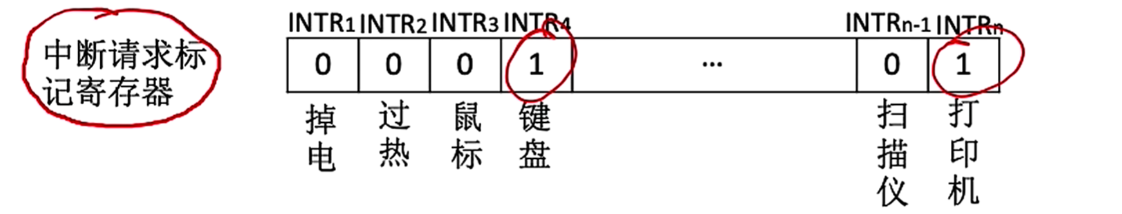

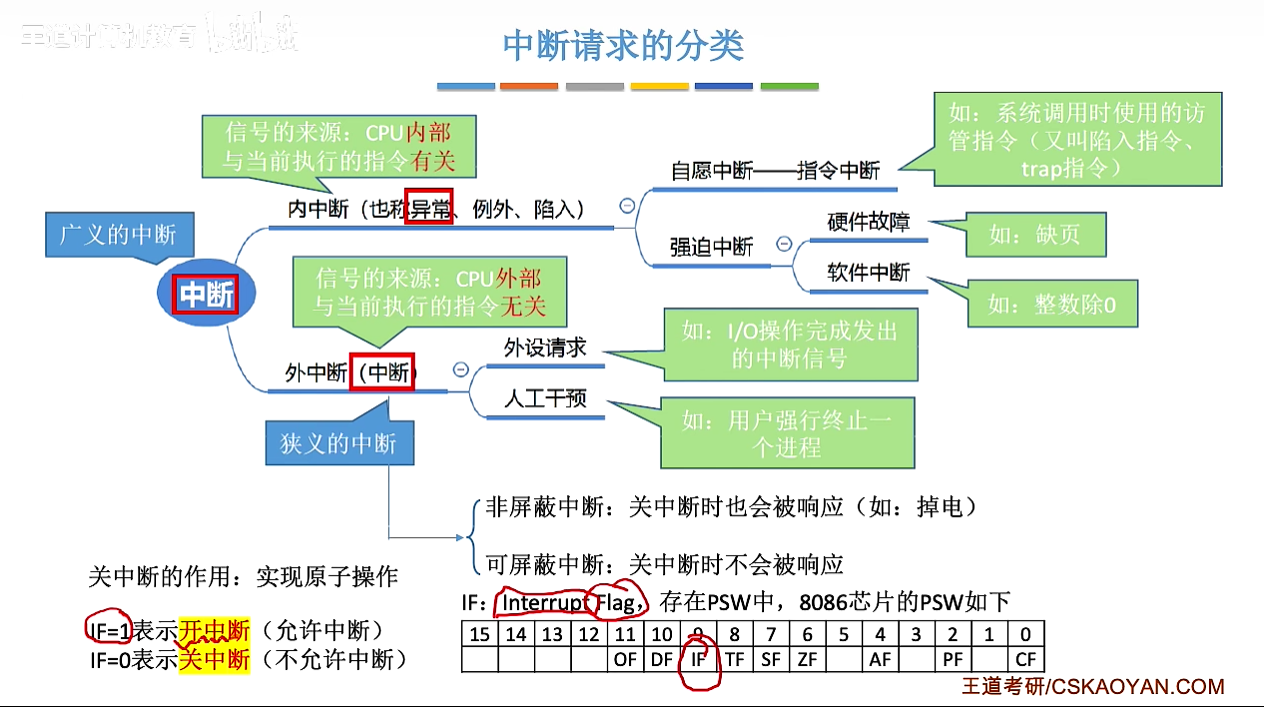

1.中断请求

- 中断源(io设备)向CPU发送中断请求信号

- 中断源如何发送请求信号?

- ==中断请求标记触发器==:①每个中断源都有一个,记录中断事件并区分不同的中断源。②“1”表示某个中断源有请求。

- 中断请求标记触发器 VS **==中断触发器==**:中断触发器是CPU内部的。负责开/关中断。一个CPU只有一个中断触发器。

2.中断响应

响应中断的条件

- 中断源有中断请求。

- CPU开中断

- 一条指令执行阶段完毕(且没有更紧迫的任务)。

中断==响应(优先级)==判优:如果响应了,而且多个请求源,需要根据判优原则响应一个中断源。

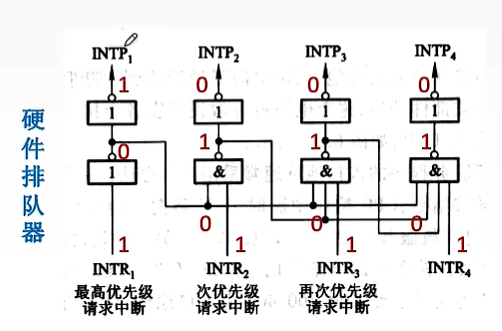

- 硬件判优(快):by硬件排队器

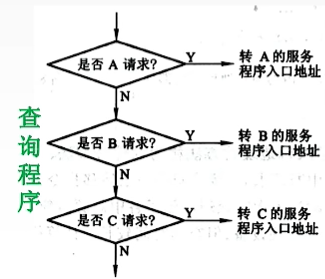

- 软件判优(慢):by查询程序

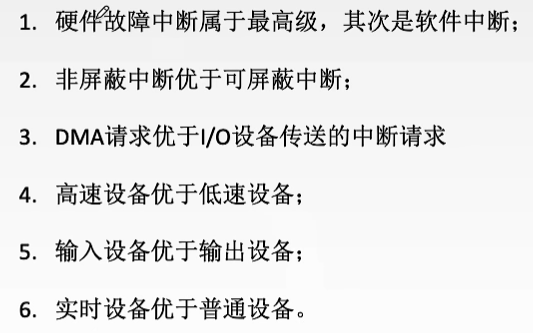

- 判优优先级固定设置:

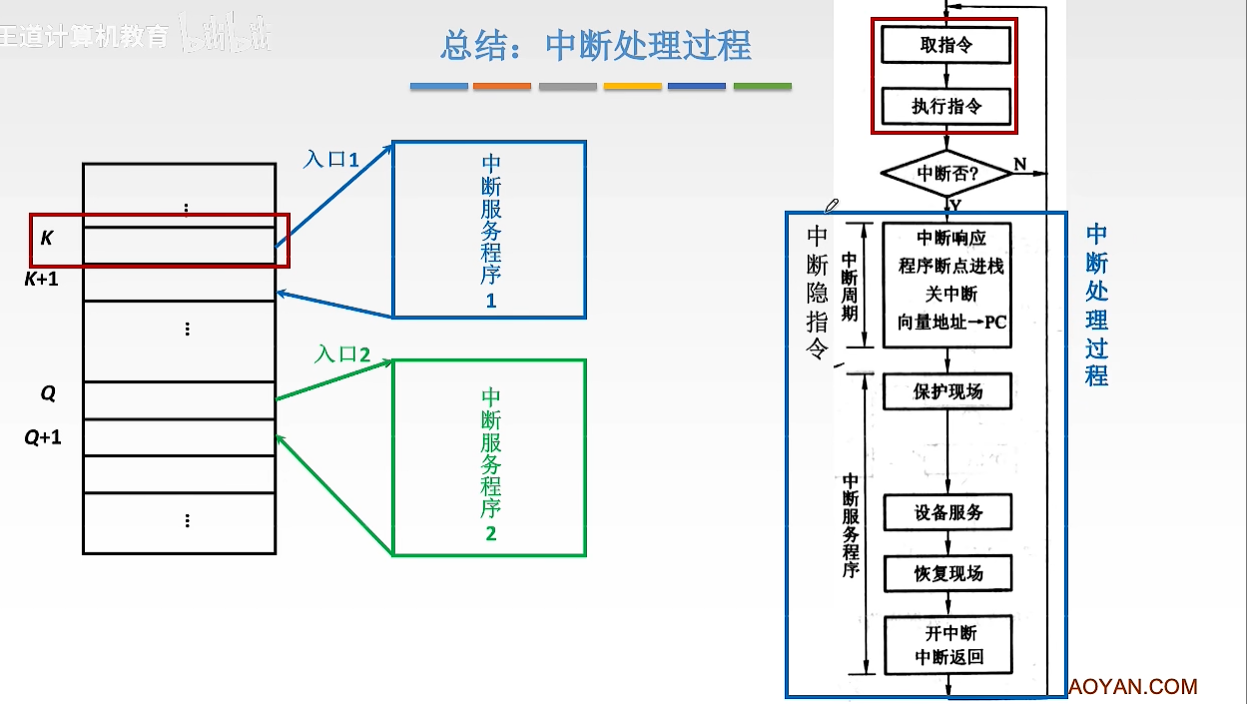

3.中断处理

==①中断隐指令==

保存PC旧值和寄存器内容(PSW),让PC指向中断服务程序的第一条指令。

由硬件自动完成,而不是软件,为了保证可靠和安全。

①关中断

②保存断点(存入堆栈或者指定单元)

==③查询中断源入口(PC指向新值)==

- 软件查询法:(非向量中断)

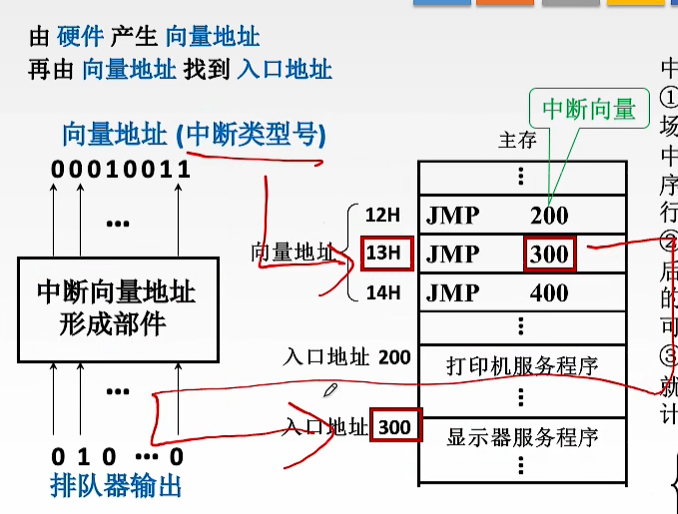

- 硬件中断向量法(指针的指针):

- (排队器输出)→中断向量地址形成部件→向量地址(内容是中断向量)→(中断向量的内容就是) 入口地址。

- (排队器输出)→中断向量地址形成部件→向量地址(内容是中断向量)→(中断向量的内容就是) 入口地址。

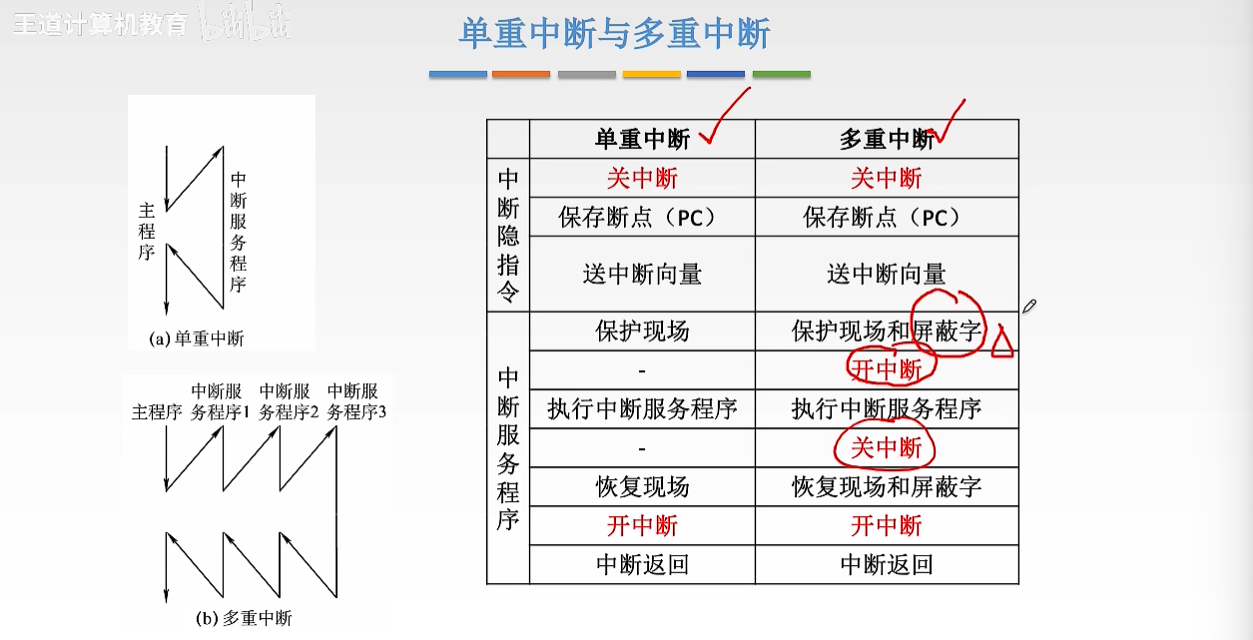

==②执行中断服务程序==

- ①保护现场(by软件完成)【和屏蔽字】 注:【多次中断用】

- 【开中断】

- ②执行中断服务(不同设备不同操作)

- 【关中断】

- ③恢复现场和屏蔽字。

- 【开中断】

- ④中断返回。【中断服务程序的最后指令是中断返回,而不是无条件转移!中断返回的不同之处还得返回寄存器的内容!】

断点和现场的对比:

- 断点的保存由硬件实现。

- 现场可被指令访问,通过软件(中断服务程序)实现保存。

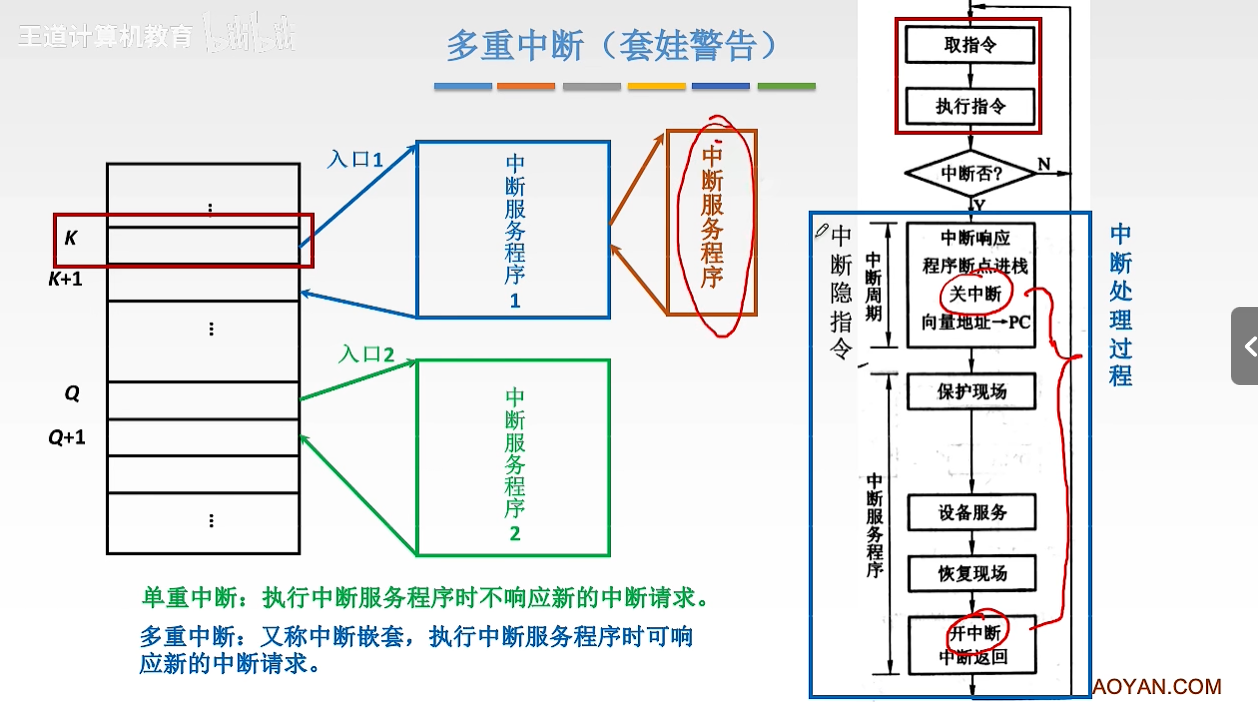

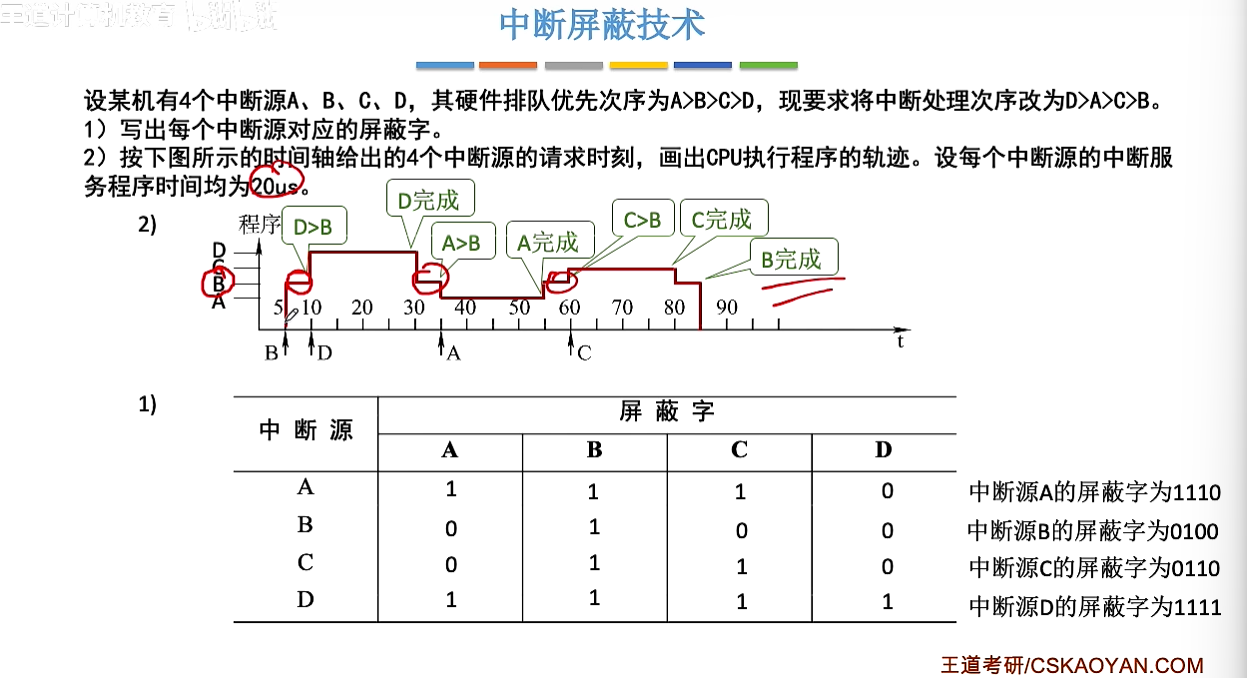

多重中断

多次中断:执行中断服务程序时,可相应新的请求。

==中断优先级==,包括 ==响应优先级== 和 ==处理优先级==。

- 响应优先级不可动态改变。处理优先级可以利用中断屏蔽技术动态调整。(决定多个中断服务程序执行完的次序)

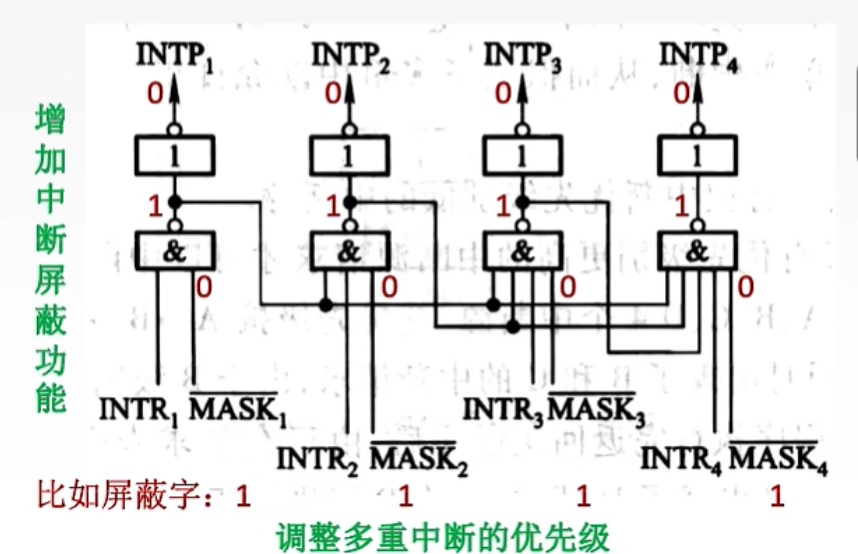

中断屏蔽技术

每一个中断源都有一个屏蔽触发器,对应一个屏蔽字

屏蔽字:可以屏蔽某些中断(eg低速设备屏蔽高速设备的中断,自己不被打扰)。

- “1”越多,优先级越高。

优点:可以调整多次中断的优先级。

CPU执行程序的轨迹

程序中断方式

1.准备阶段:当IO设备在准备(外部设备)数据的时候,CPU执行现行程序。

2.请求阶段:IO设备准备好后,会给CPU发送中断请求(信号)。

3.响应阶段:CPU执行完当前指令(地址K的指令)后

- CPU执行中断隐指令:关中断。保存断点。引出中断服务程序(找到入口地址送PC)

4.执行中断服务程序:

- 保护现场

- 执行IO传送

- 恢复现场

- 返回主程序

5.继续执行:CPU从断点(原程序K+1)继续执行主程序。外设开始准备下一个数据。

程序中断方式缺点:虽然说CPU不用等待了,但是会被频繁打断(尤其是高速外设)

小结

DMA方式

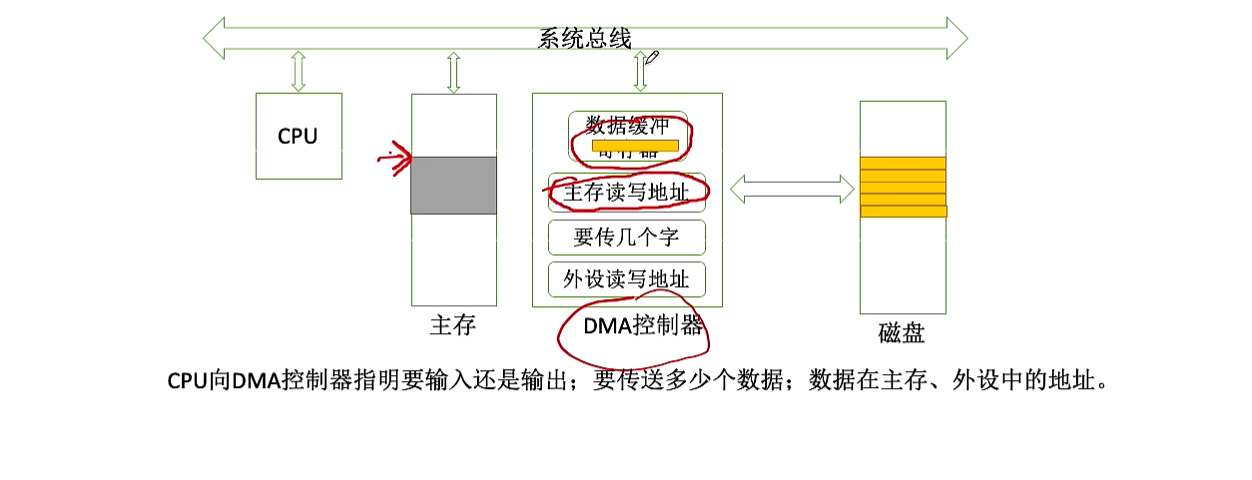

DMA控制器

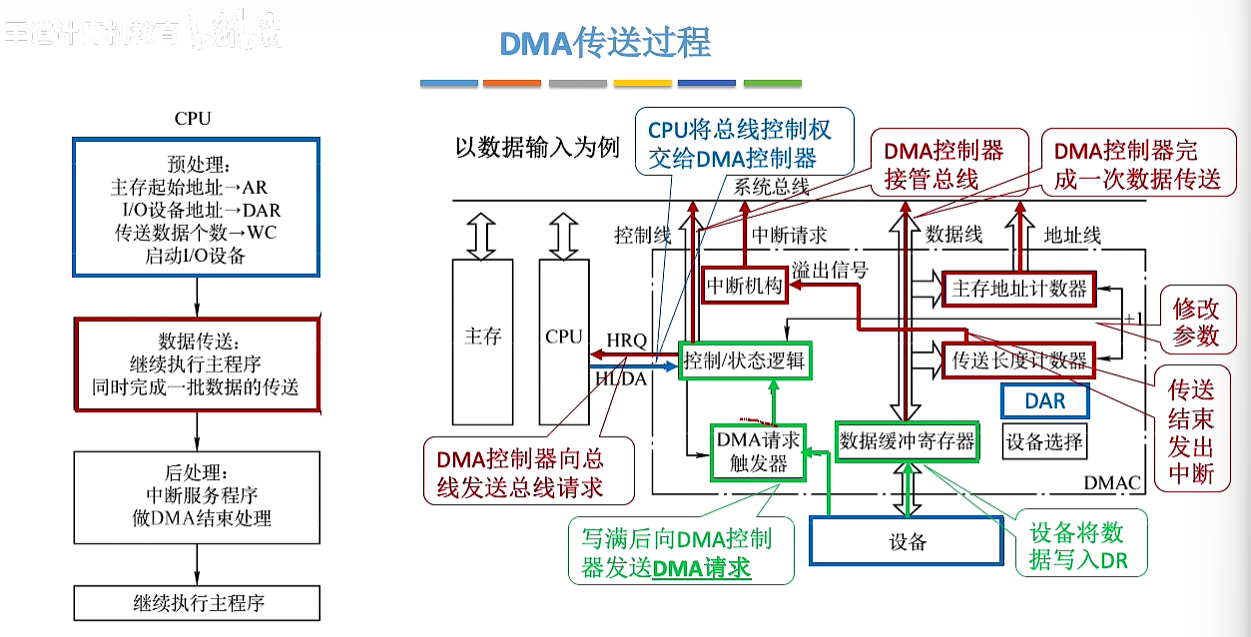

==工作流程(DMA控制器)==

预处理:

- 请求: 当**==外设==准备好传送数据*(如输入数据已准备好或可接收新数据)时,会向DMA控制器==发送DMA请求**==。

- 接管: DMA控制器收到请求后,会向CPU发送总线请求(希望占用总线)。

- 响应: CPU在当前总线周期结束后(若支持,则在**==总线周期/机器周期/总线事务末尾==响应),向DMA控制器发送总线响应**信号,并释放总线控制权(CPU暂停访存)。

- 控制: **==DMA控制器接管总线控制权==**,进入DMA操作周期。

数据传送:

- 寻址: DMA控制器将内部地址寄存器中的主存地址送上地址总线,用于定位数据在内存中的位置。

- 计数: 每次传送一个数据字后,DMA控制器会自动修改(递增或递减)主存地址计数器,并递减传送长度计数器。

- 控制: 根据操作类型(DMA读/写),DMA控制器发出I/O读或写信号控制外设,同时发出存储器写或读信号控制内存。数据直接在外设与内存之间传送,无需经过CPU。

后处理:

- 检测: DMA控制器检测到传送长度计数器的值变为零(或外部传送结束信号),表示预定的==数据块==已传送完毕。

- 通知: DMA控制器向CPU发送DMA中断请求信号,通知CPU数据传送已完成。

- 处理: CPU响应中断,执行==中断服务程序==做DMA结束处理。

- 恢复: 中断服务程序返回后,CPU继续执行之前被打断的主程序。

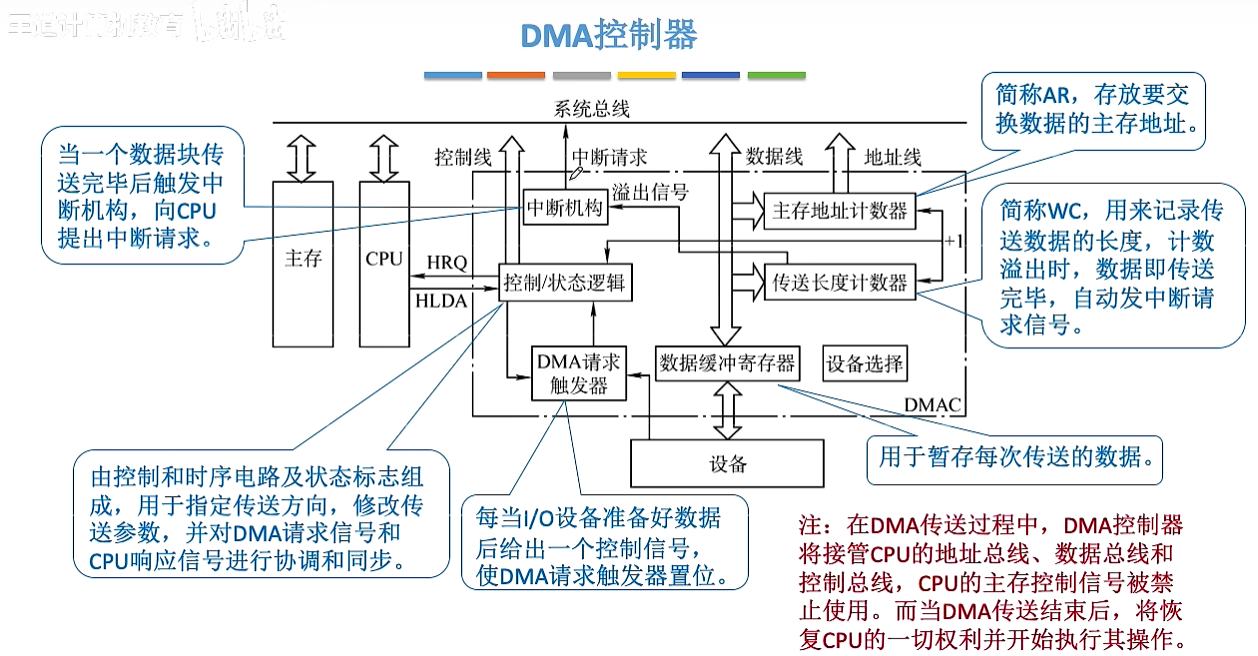

DMA控制器的结构

结构:中断机构。控制/状态逻辑。DMA请求触发器。主存地址计数器。传递长度计数器。数据缓冲寄存器。

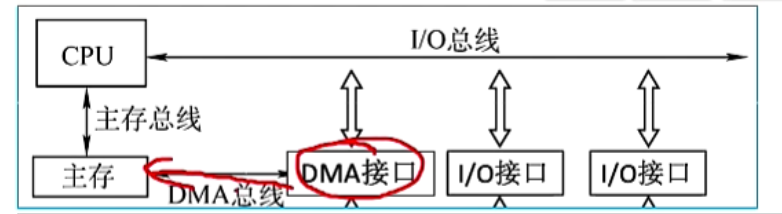

三总线结构下的访存冲突

-- CPU和DMA控制器的访存冲突,如何解决?

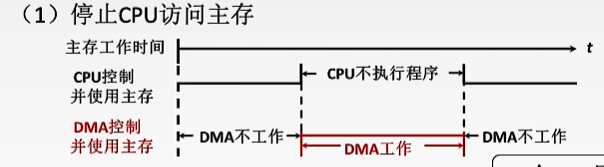

a.停止CPU访问主存(DMA接口向CPU发出停止信号,完成了再通知)

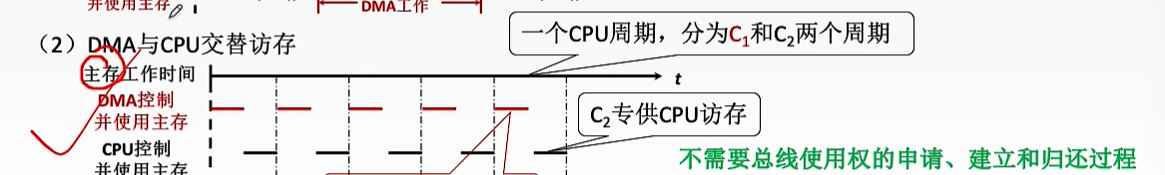

b.DMA和CPU交替访存

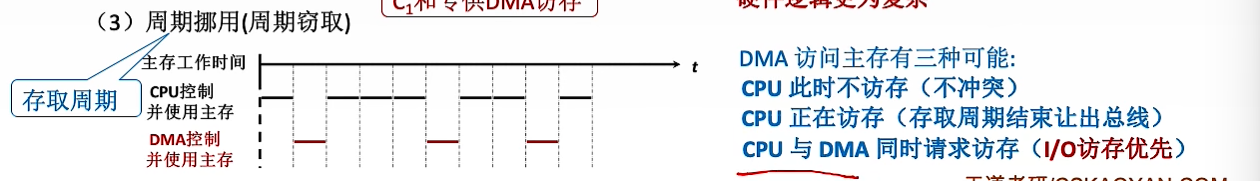

c.周期挪用(周期窃取)(主存**==存取周期==**)

- IO设备需要访存的时候,挪用一或多个存取周期

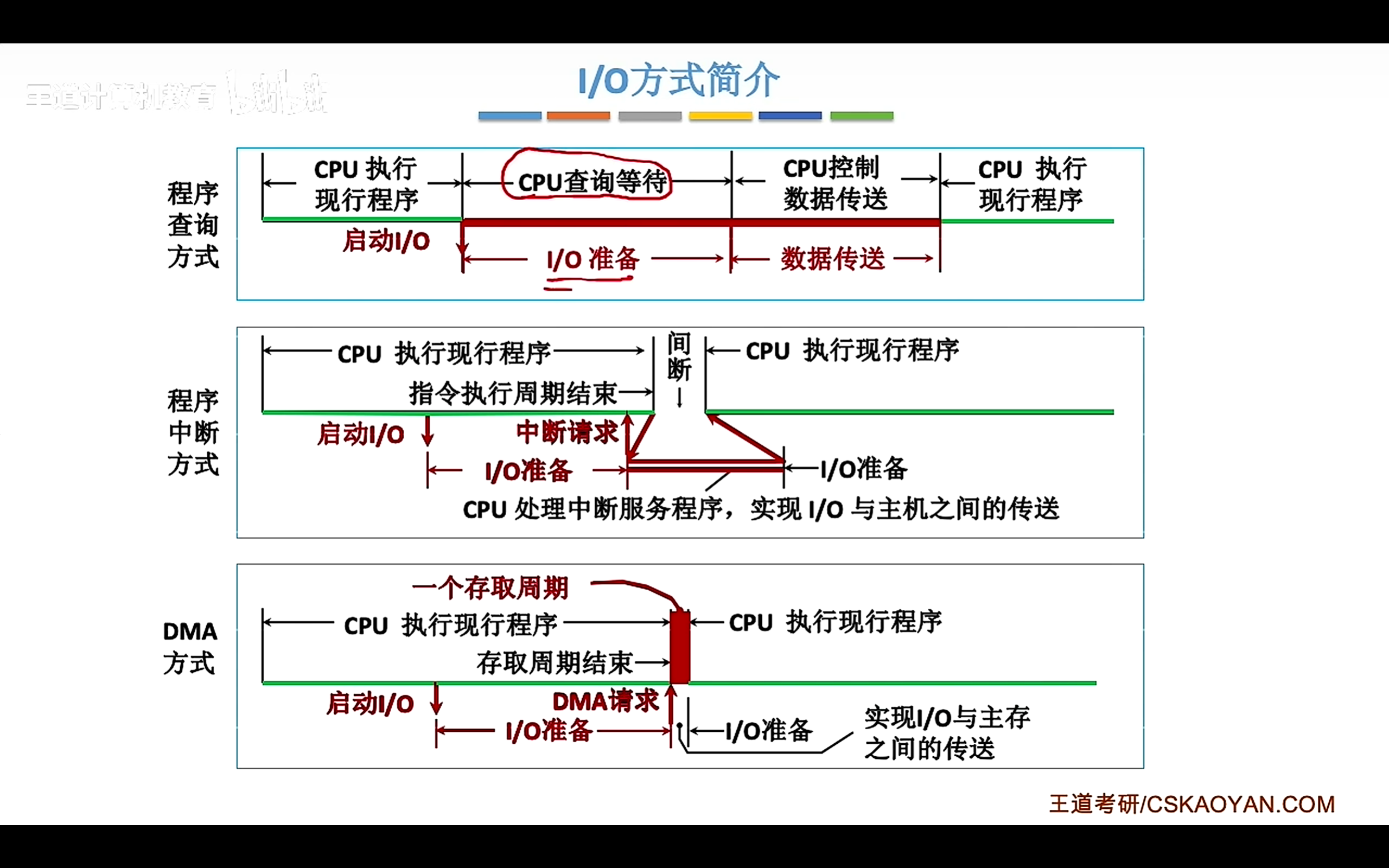

三种IO控制方式对比

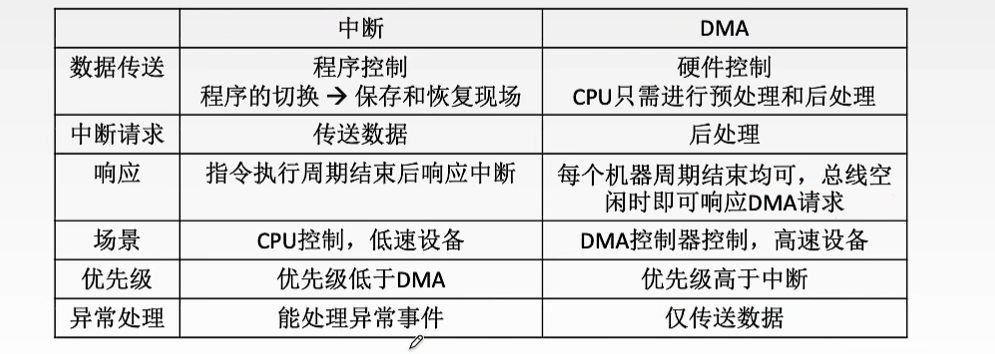

- DMA的数据传送是硬件控制(即CPU只需进行预处理和后处理)。中断的数据传送是程序控制(要有保存和恢复现场)。

- ==DMA的响应,在每个机器周期(总线周期?)结束==均可【取址间址等之后均可】,总线空闲即可响应DMA请求

| 程序查询方式 | 中断方式 | DMA方式 |

|---|---|---|

| CPU与外设串行工作,传送与主程序串行工作 | CPU与外设并行工作,传送与主程序串行工作 | CPU与外设并行工作,传送与主程序并行工作 |

| 一次传输一个字 | 一次传输一个字 | 一次传输一个数据块 |

| – | 外设准备时间 必须大于等于 中断处理时间 | – |

| both | : | 在数据传送的底层,主存地址加1、计数器减1 |

异常和中断小例子

访存缺页(虚拟存储器失效),内部异常。

定时器到时,外部中断。

网络数据包到达,外部中断。

cache缺失,no,正常现象。

浮点数下溢:no,当作机器零处理。

浮点数上溢:中断(超过浮点数表示范围)