计组-6.1 总线概述

6.1 概述

基本概念

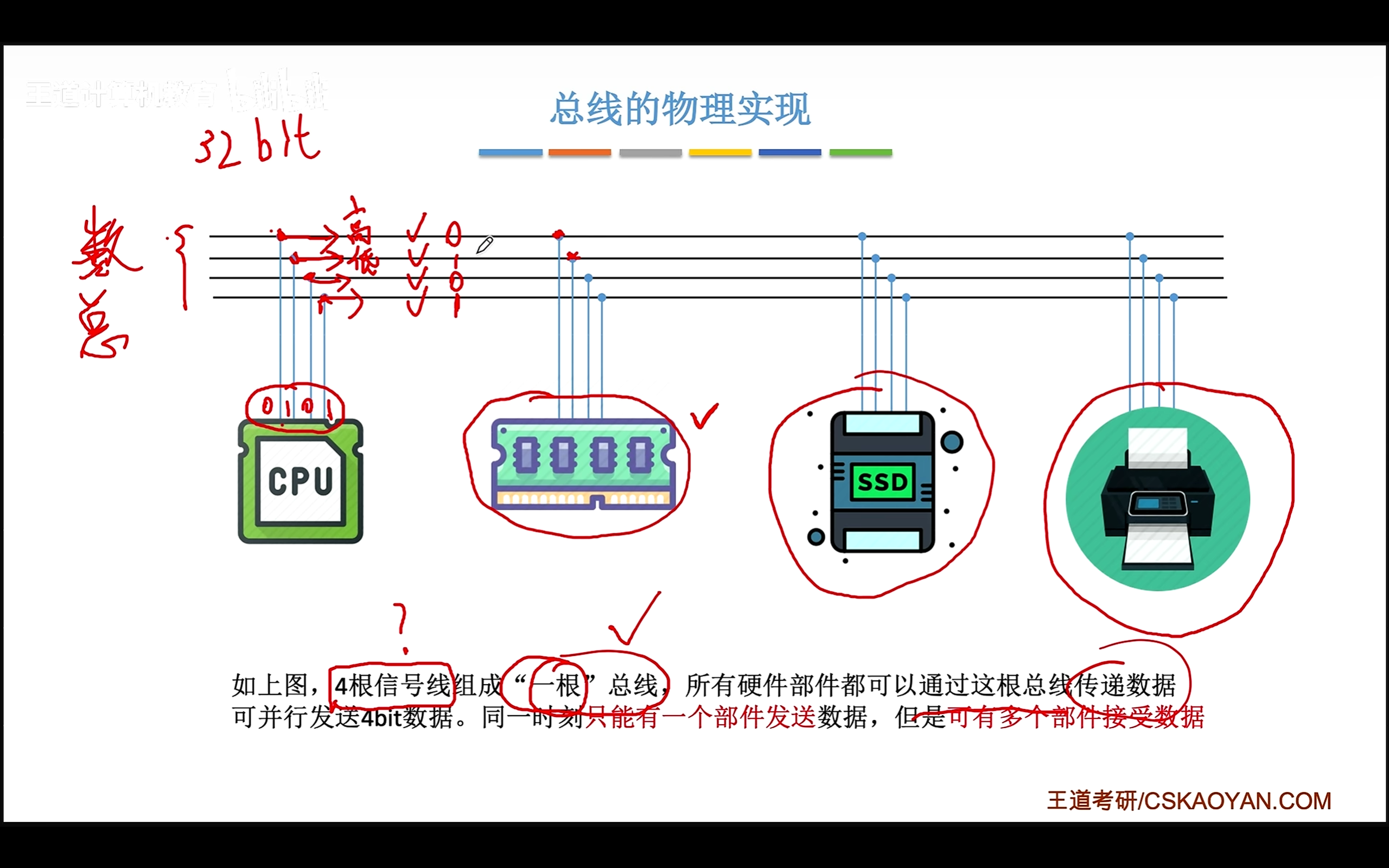

- 总线是一组能为多个部件 ==分时 共享== 的公共信息传送线路

- 总线的由来:

- 早期外部设备少,用的是分散连接方式

- 后来外部设备多,采用总线连接方式

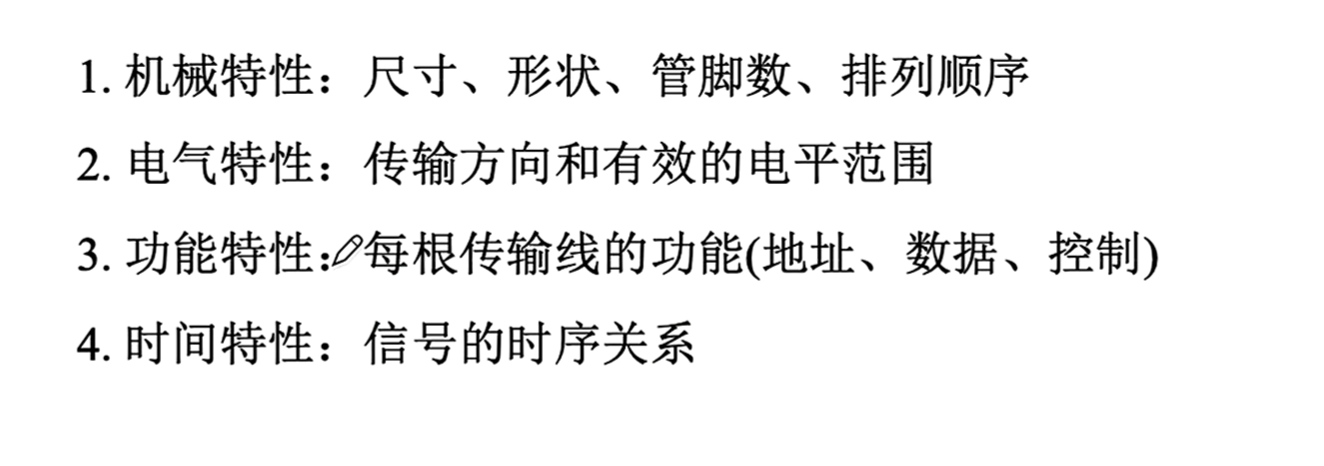

(设计)总线的特性

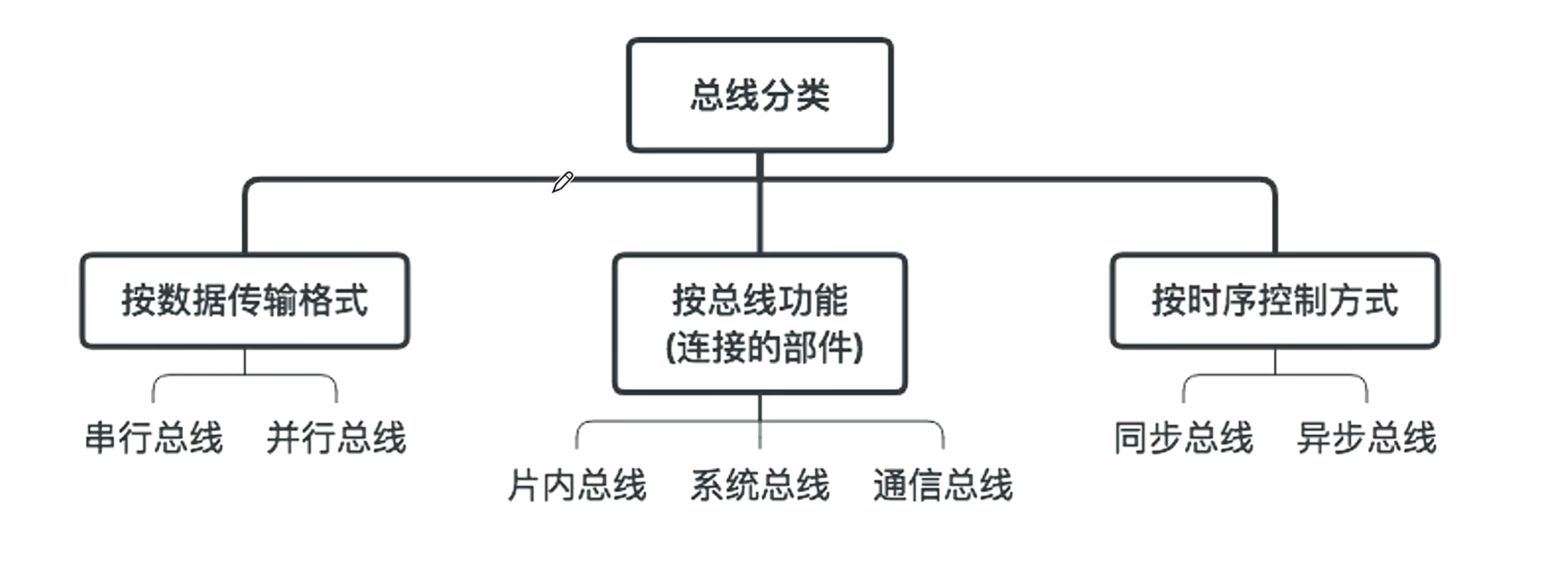

总线的分类及经典结构

A.按数据传输格式

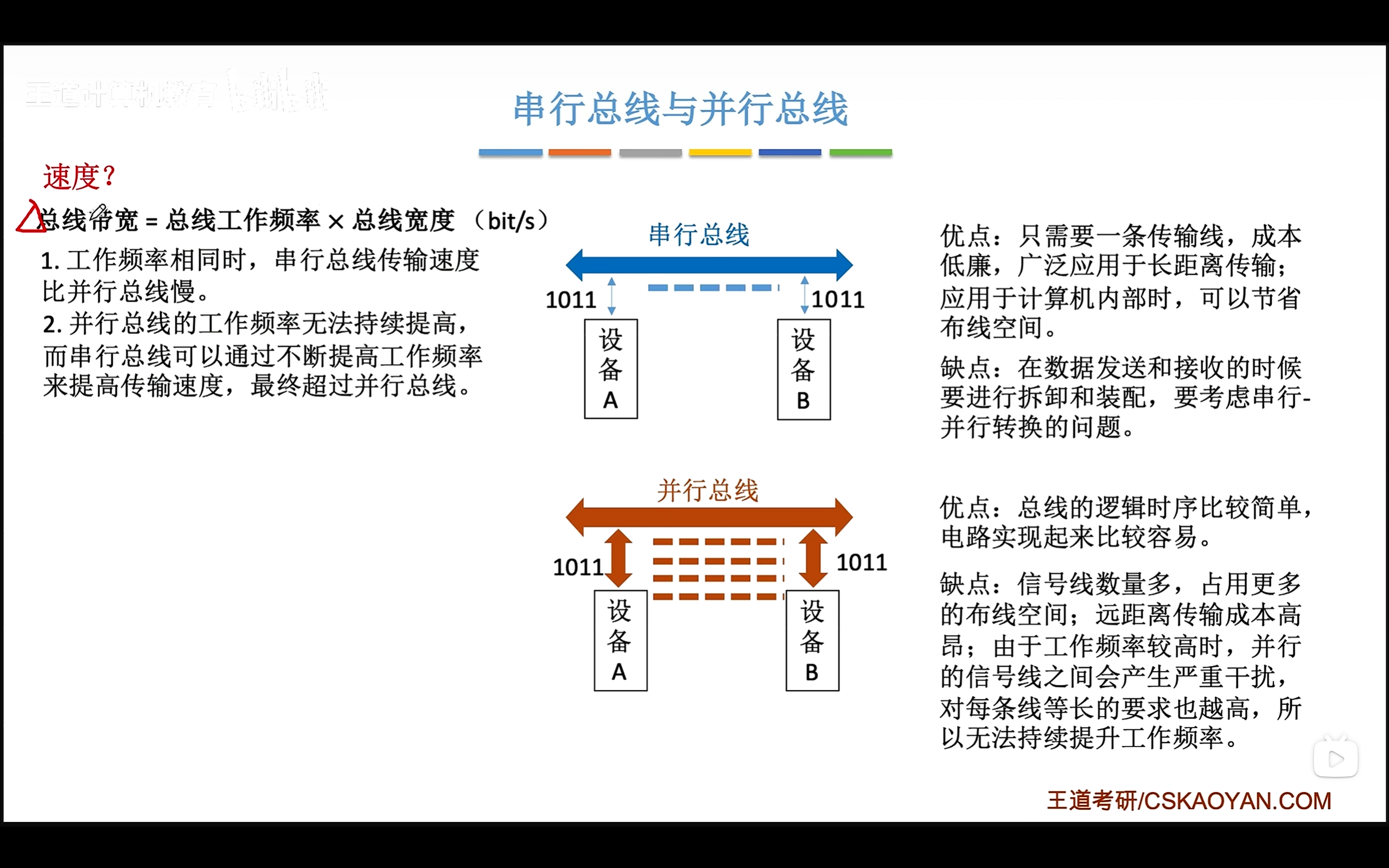

串行总线:

- 一次发送一个位(bit)

- 优点:成本低(只用一根),适用于长距离传输

- 缺点:数据收发需要进行串行-并行转换。(eg电脑内部一次发送的数据一般是64位)

- attention:

- 串行:强调的是 *”一位一位传输”*(物理层面)

- 复用:强调的是 *”多个功能共享同一套线路”*(逻辑层面)

并行总线:

- 一次能并行发送很多个位(eg数据总线就是并行总线)

- 优点:总线的逻辑时序简单,电路实现容易。

- 缺点:布线空间大。远距离传输成本高。工作频率不能太高(or造成不同线的数据有的到了有的没到)。高频数据线干扰。

- 造成的问题:并行总线不一定比串行总线快 (v = 数据线宽度*频率)

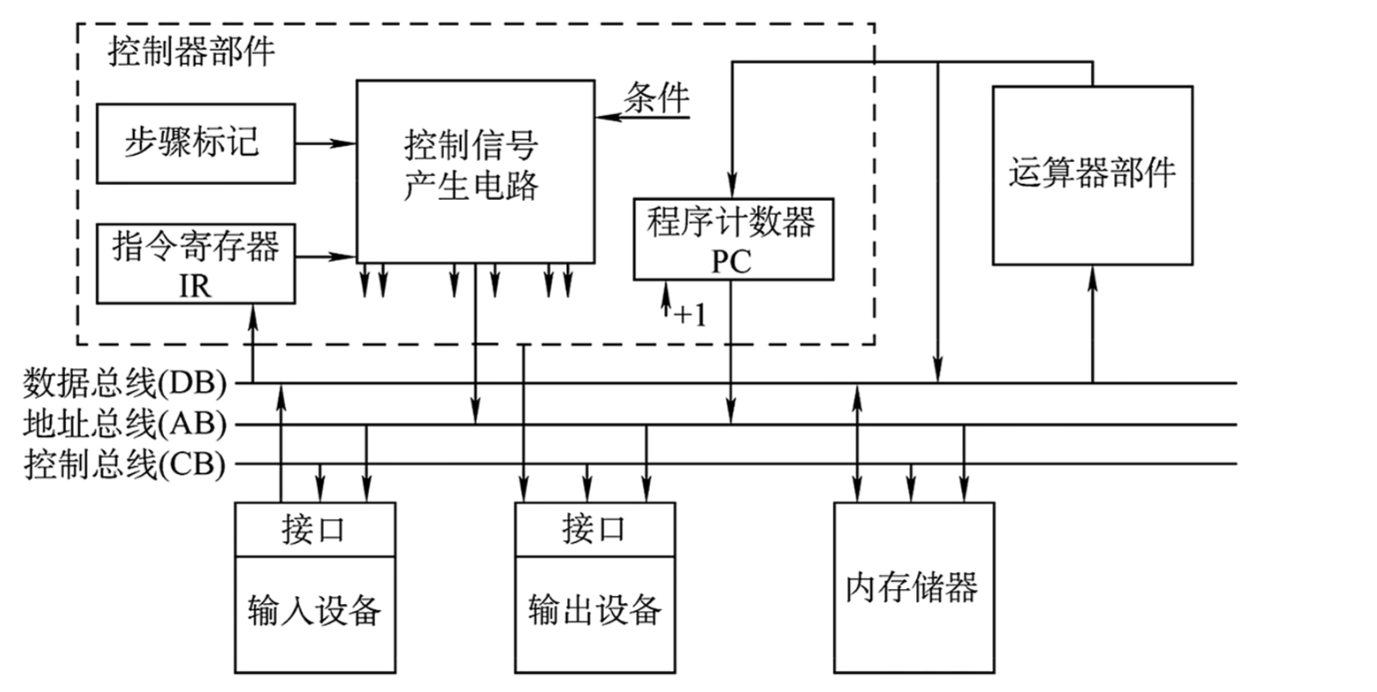

B.按总线功能

a.片内总线:CPU内部的总线

c.通信总线:连接计算机与计算机之间的总线

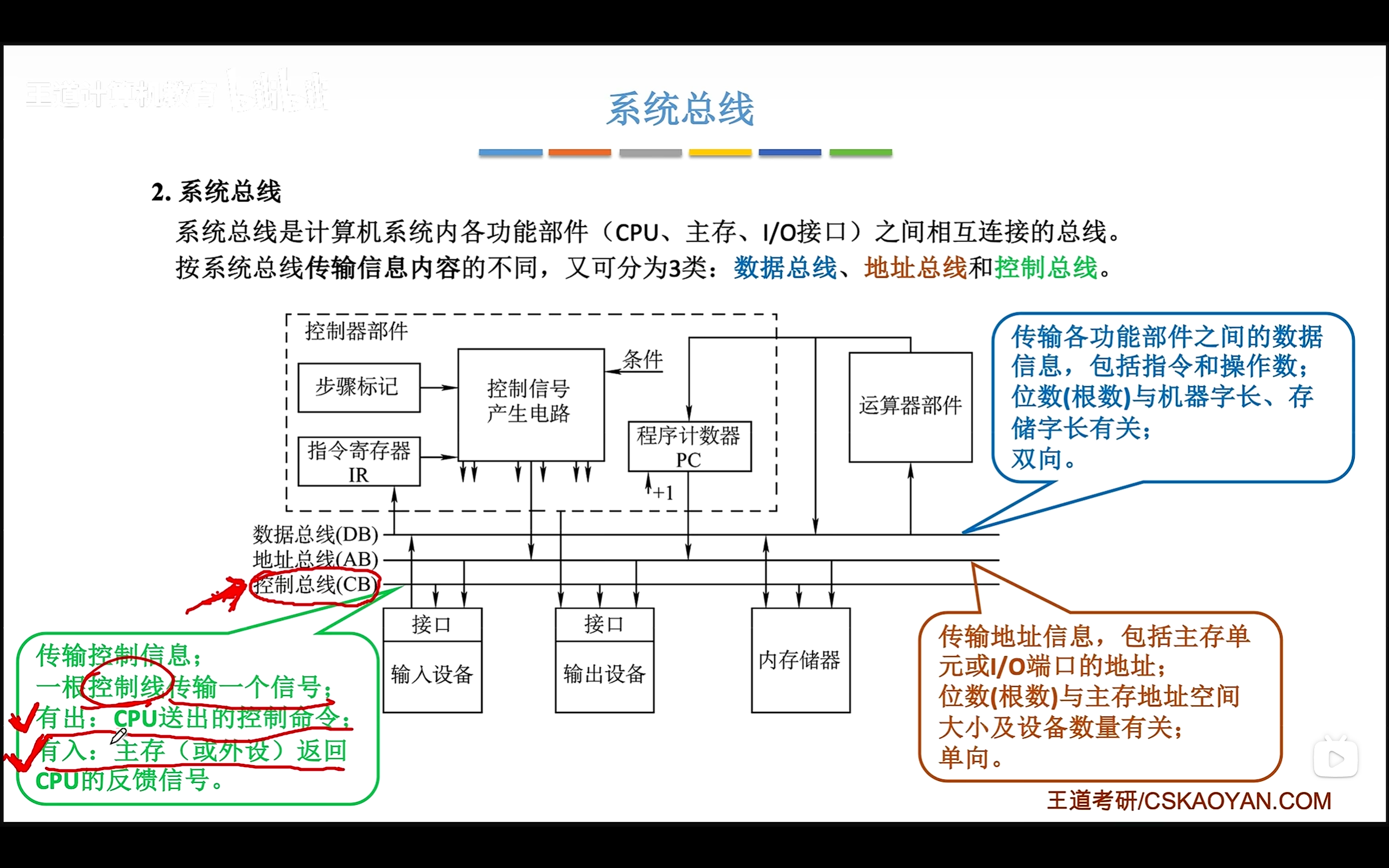

b.系统总线:计算机内部之间相互连接的总线

数据总线:

- ==传输数据信息(指令,操作数)==

- 位数 与 机器字长,存储字长有关。(==机器字长意味着指令一次就能取出来,不用两次。 ==存储字长意味着存储的数据一次就能取出来)

- 双向

- 区分:

- 数据通路是数据流经的路径(是虚拟的)

- 数据总线是实体的媒介。

地址总线

- 传输地址信息

- 位数 与 主存地址空间和设备数量有关(if有设备,地址空间=max(主存位数,设备位数))

- 单向

控制总线

传输控制信号

有出:CPU送出的控制命令

有入:主存(或外设)返回的控制信号。(eg键盘的输入打断CPU的工作)

一根看是单向,整体看是双向。(整体一部分是焊死的朝A一部分是焊死的朝B)

- 控制信号:CPU→设备

- 状态信号:设备→CPU

控制总线是总线中最复杂、最能体现“控制”精髓的部分。它除了读写命令、中断请求,还包括时钟信号、复位信号、总线请求和允许、DMA响应等等

C.系统总线的结构

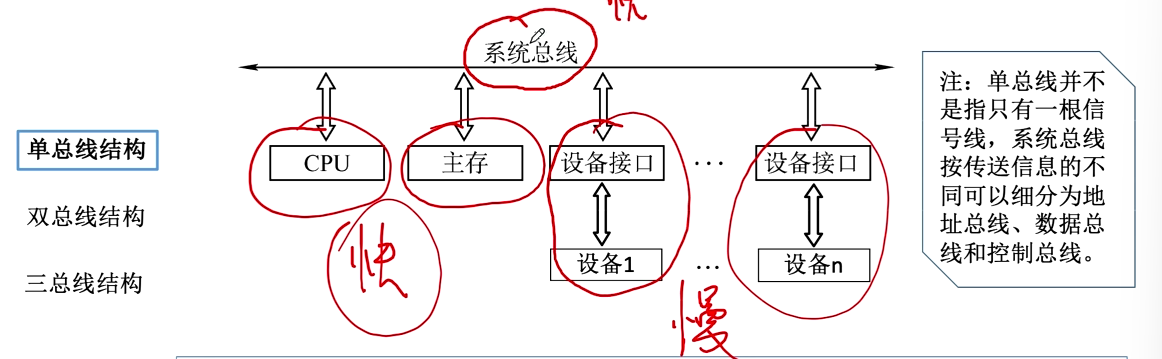

单总线结构

- ==一组==总线接到计算机内部

- 优点:结构简单成本低。易于接入新的设备。

- 缺点:①带宽低。②负载重,多个设备只能争用唯一的总线。③且不支持并行传送操作。④且因为io传输慢而总线被迫降速。

- 故而产生了双总线结构。

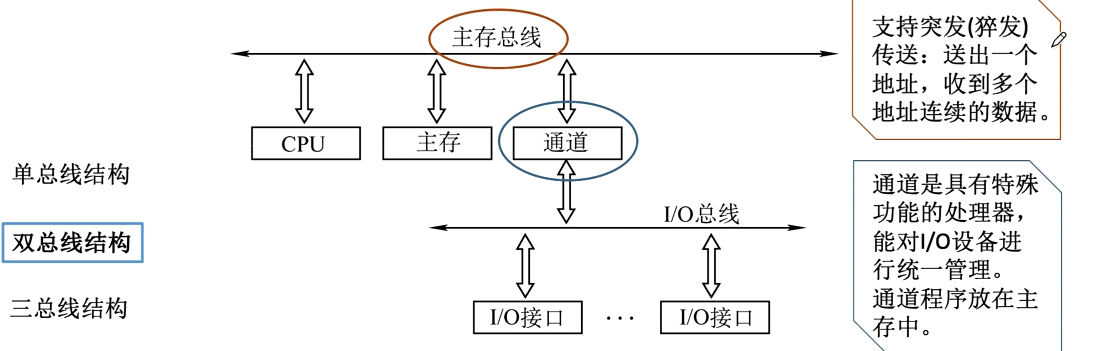

双总线结构

- 通道:小CPU,管理IO设备。

- CPU内存和通道三个传输快的连接到主存总线

- 主存总线,支持 突发 操作(只传送一次地址,之后从主存收到连续几个数据)

- IO设备(传输慢)连接到IO总线

- 优点:fast

- 缺点:需要增加通道等硬件设备。

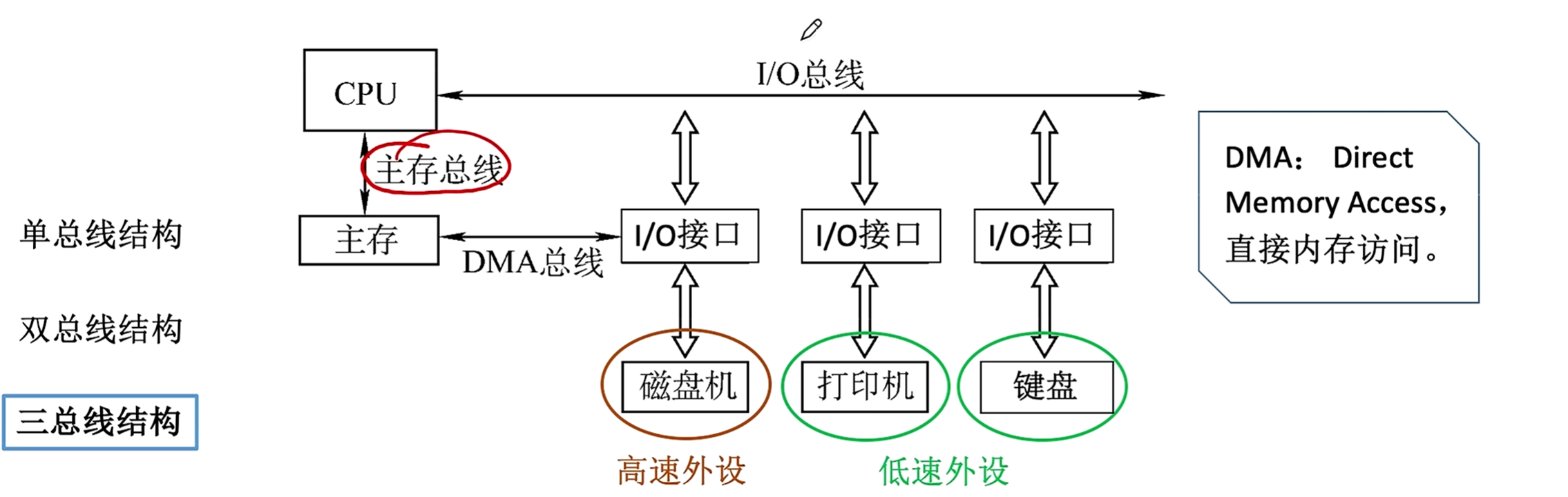

三总线结构

- 增加了主存和高速外设的DMA总线

- 优点:提高了IO设备的性能,高速有DMA总线,低速是直连的(相比于通道)。提高系统吞吐量(高速)

- 缺点:系统工作效率较低(三条IO总线,一次工作一个)

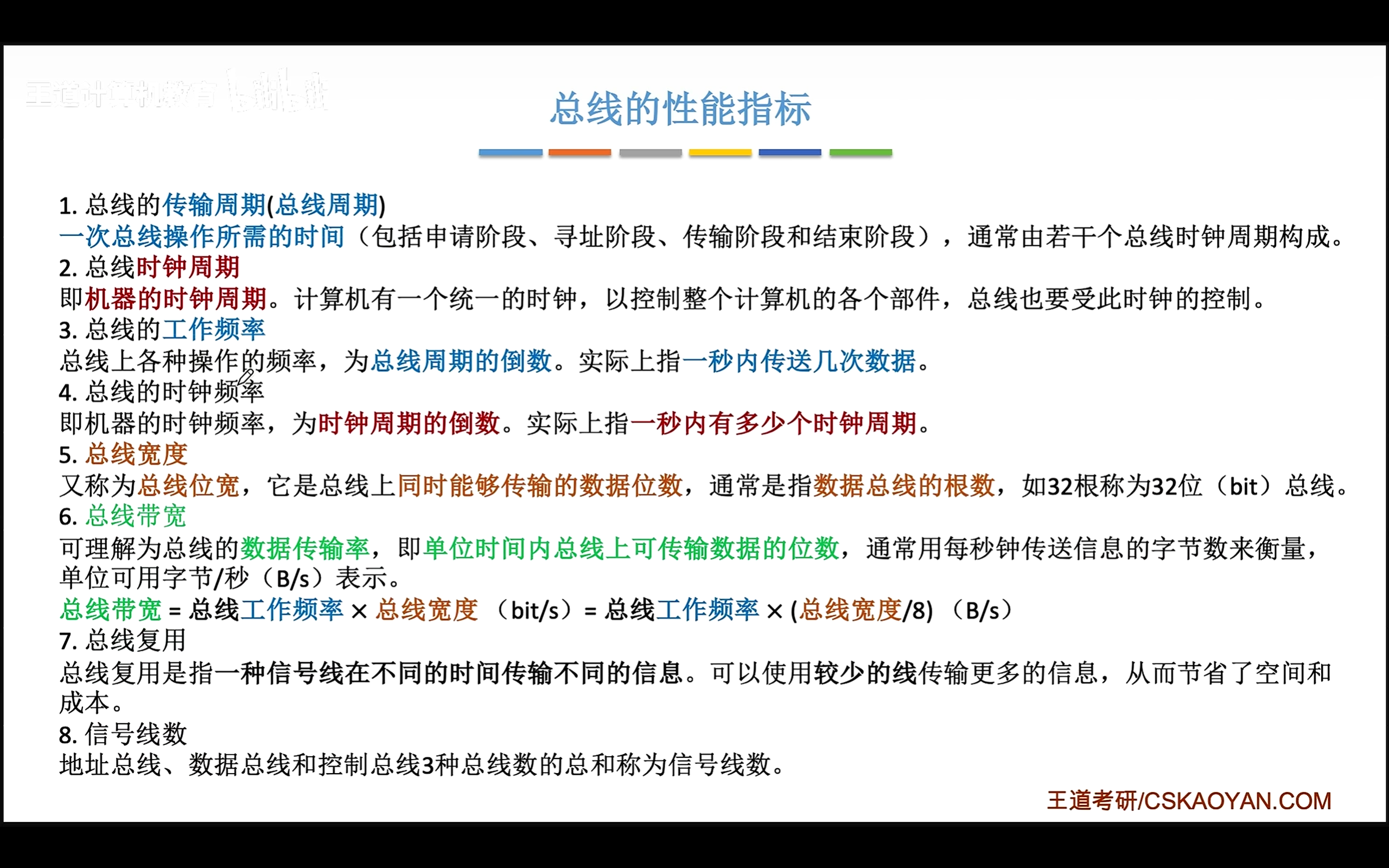

性能指标

1.总线的传输周期(==总线周期==)

- 一次总线操作所需的时间。

- 4个阶段(申请,寻址,传输,结束)

- 通常一个总线周期包含多个时钟周期

- 少数,一个总线周期对应一个时钟周期

- 少数,一个时钟周期对应多个总线周期(就像超流水一样)

2.总线时钟周期

- == 机器时钟周期

3.总线的工作频率

- == 总线周期的倒数

- 即一秒内传送几次数据

4.总线的时钟频率

- == 总线时钟周期的倒数

- 即一秒内有多少个时钟周期

5.总线宽度

- 位宽(一次能同时传输多少个数据位)

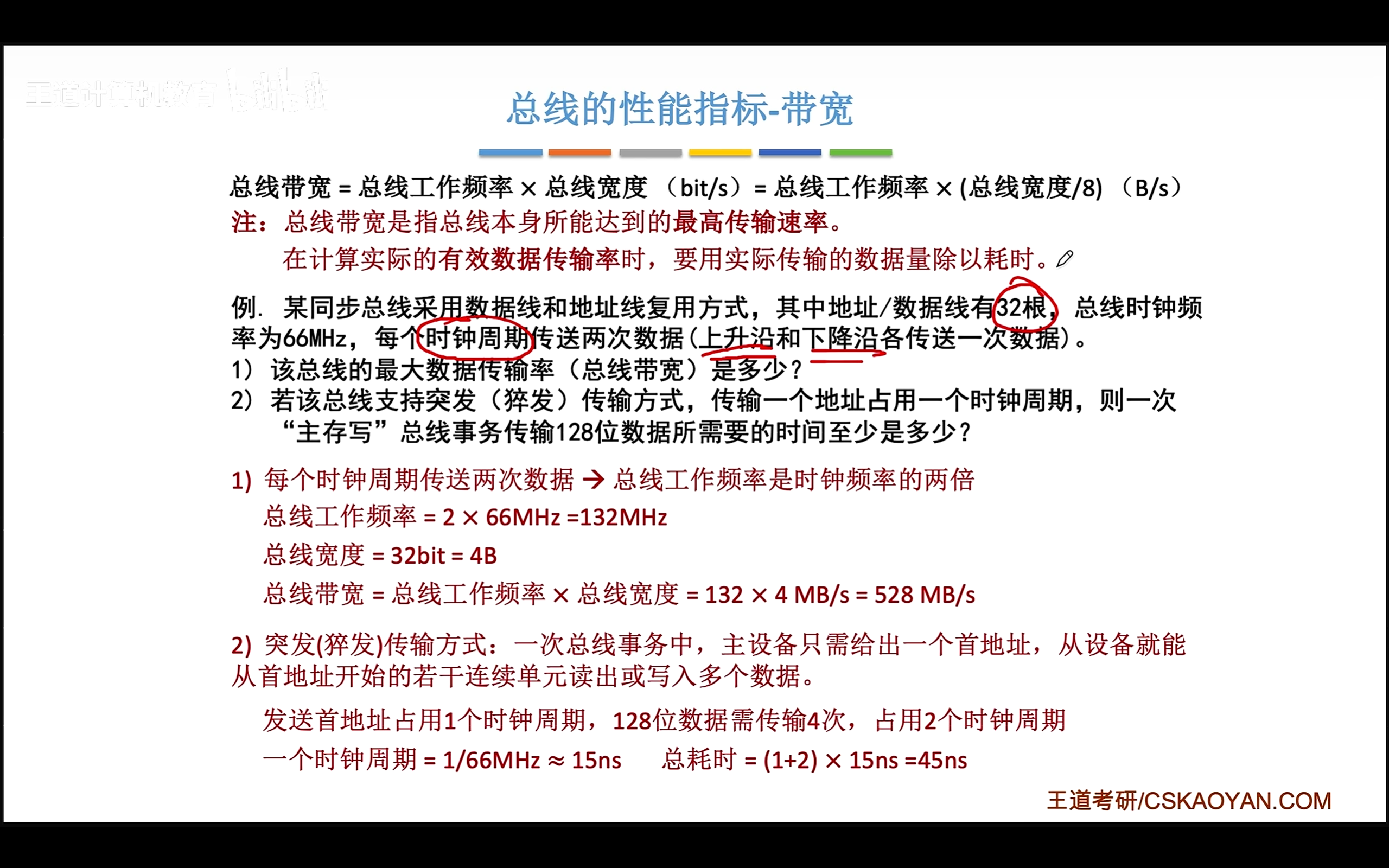

6.总线带宽

- 总线每秒能传送多少数据

- 通常是数据总线的宽度

- ==总线带宽 == 总线工作频率 * 总线宽度(bit/s)⭐==

- 此处是最高速率。有效速率得用 实际传输数据量/t

7.总线复用

- eg地址总线和数据总线复用

8.信号线数

- 信号线的最小的传输线(收发1bit)

- 信号线数 == 数据信号线数+地址信号线数+控制信号线数(以系统总线为例)

评论