计组-5.0 前言

发表于|更新于|计组

|浏览量:

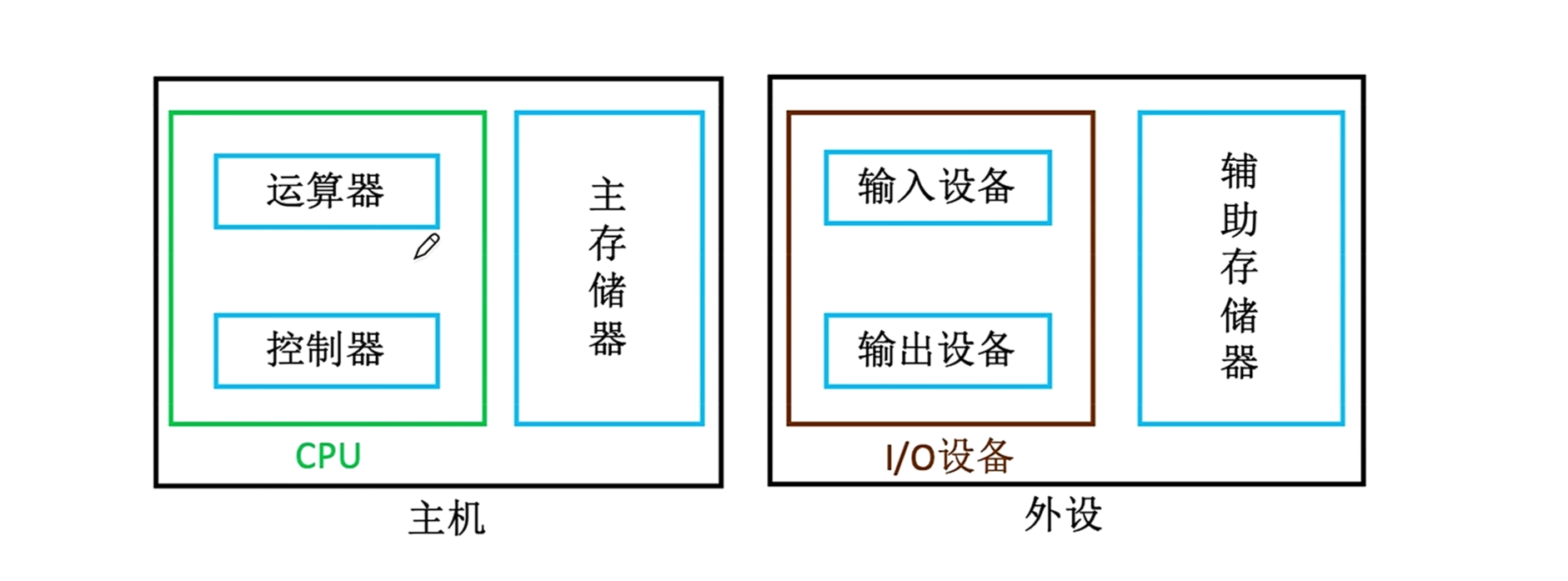

计算机与CPU组成

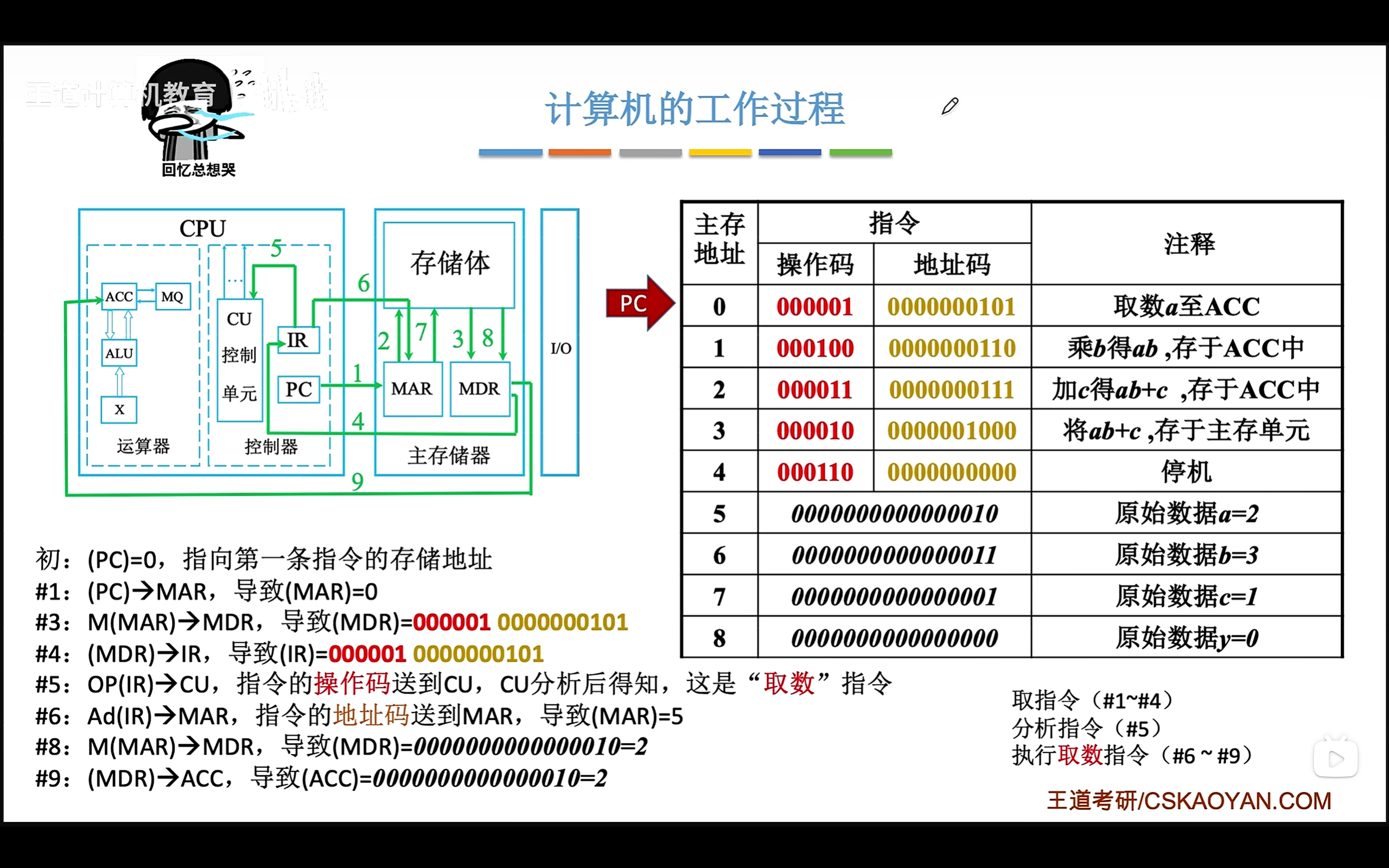

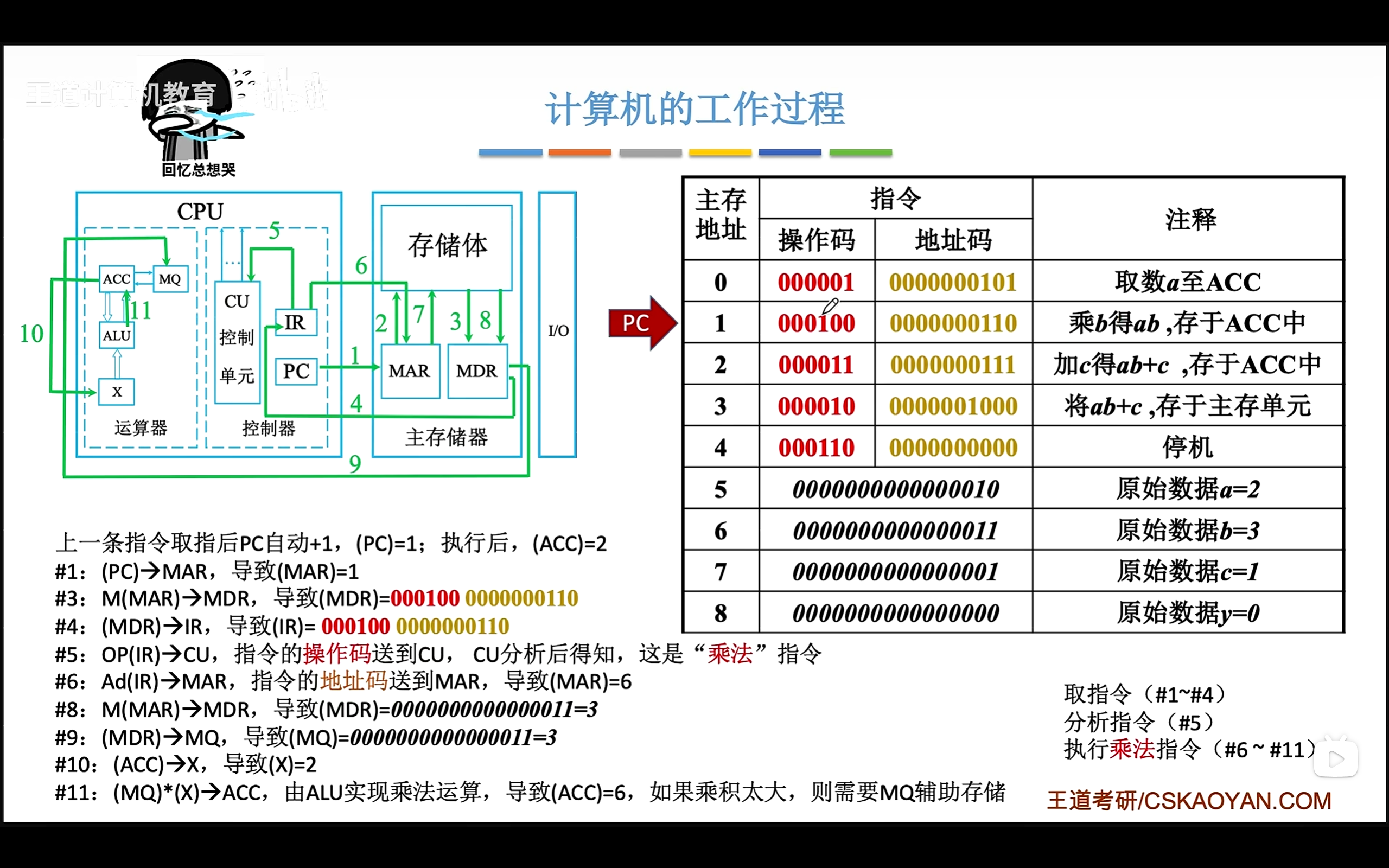

计算机的工作过程

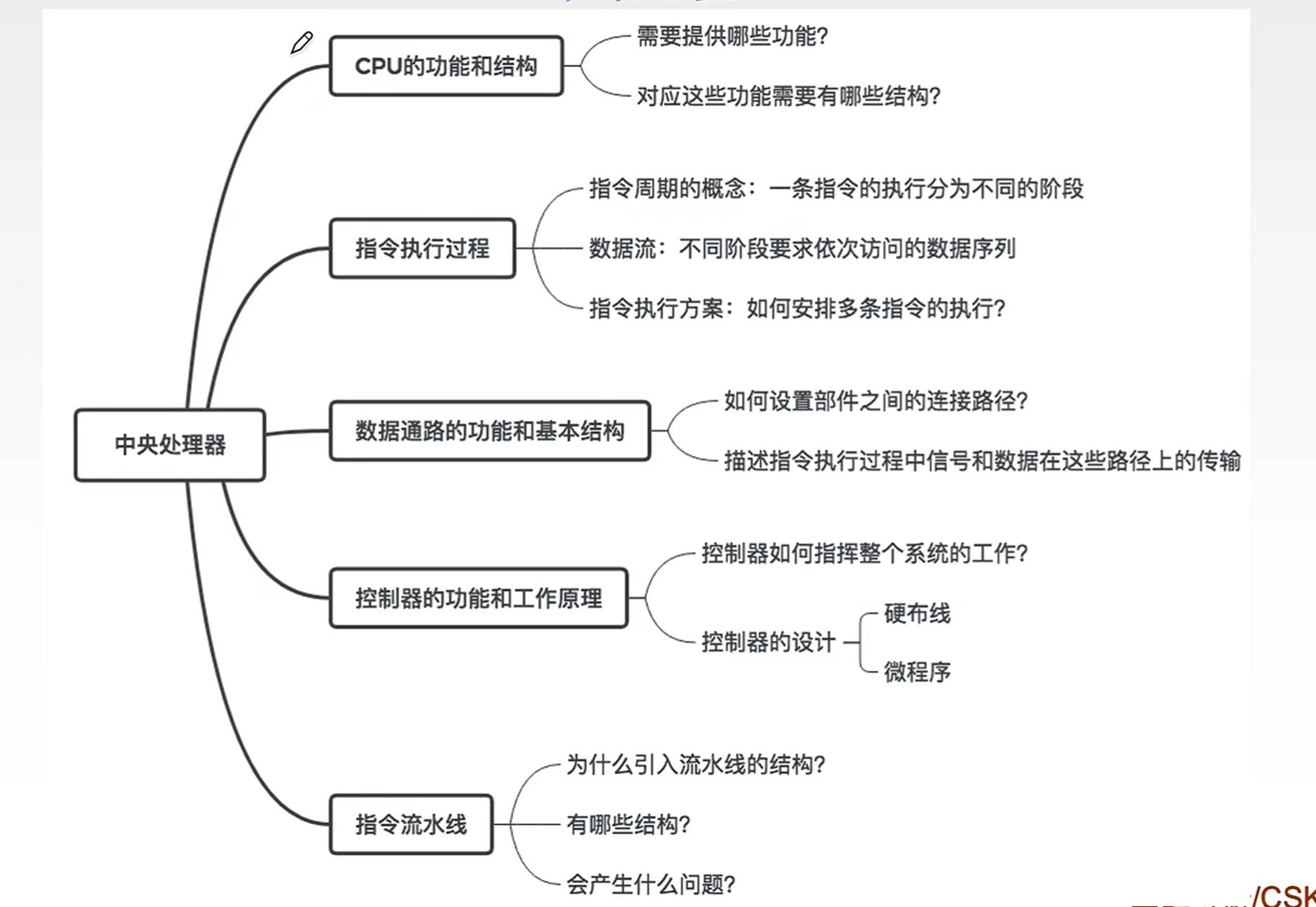

第五章总览

相关推荐

2026-03-02

计组-5.1 CPU的功能和基本结构

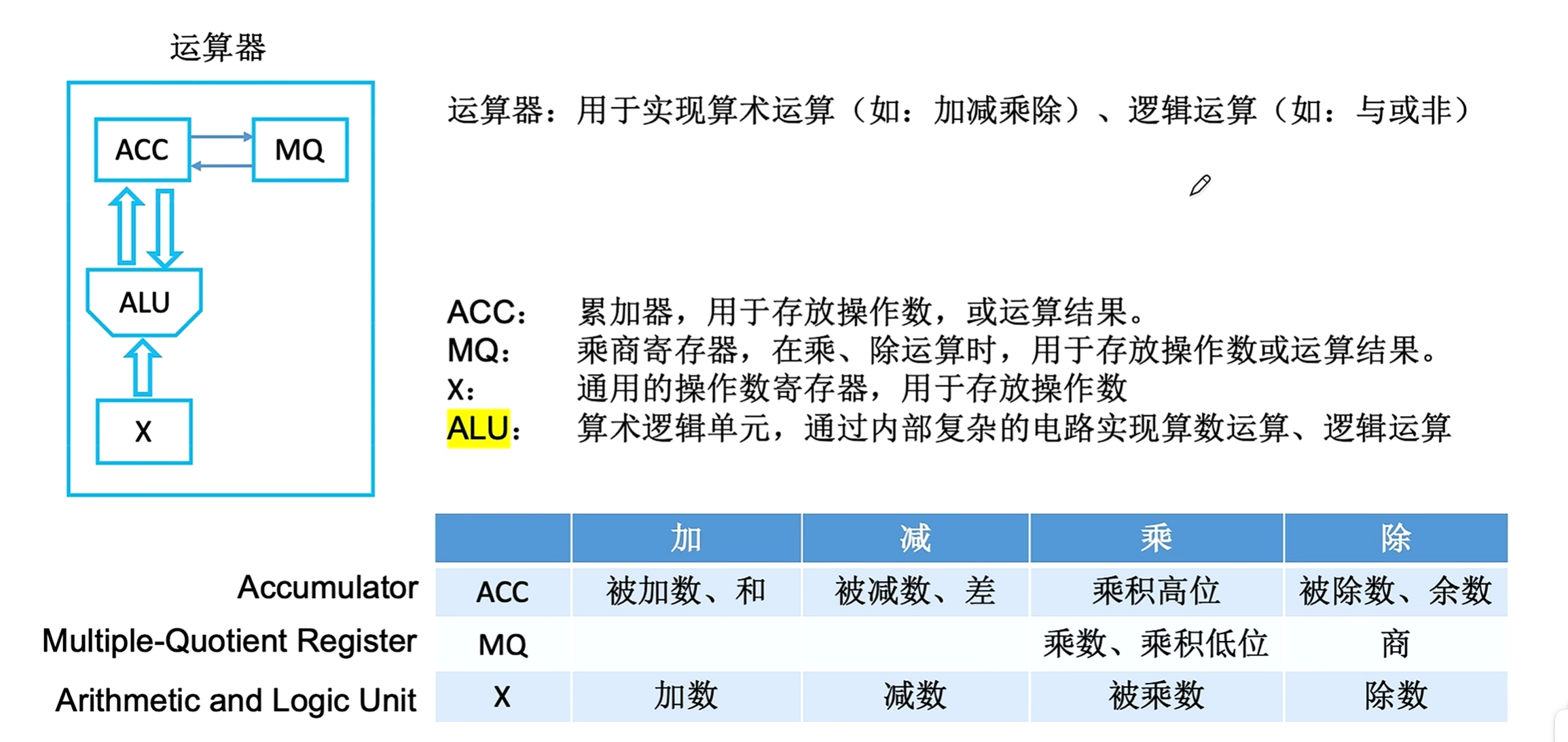

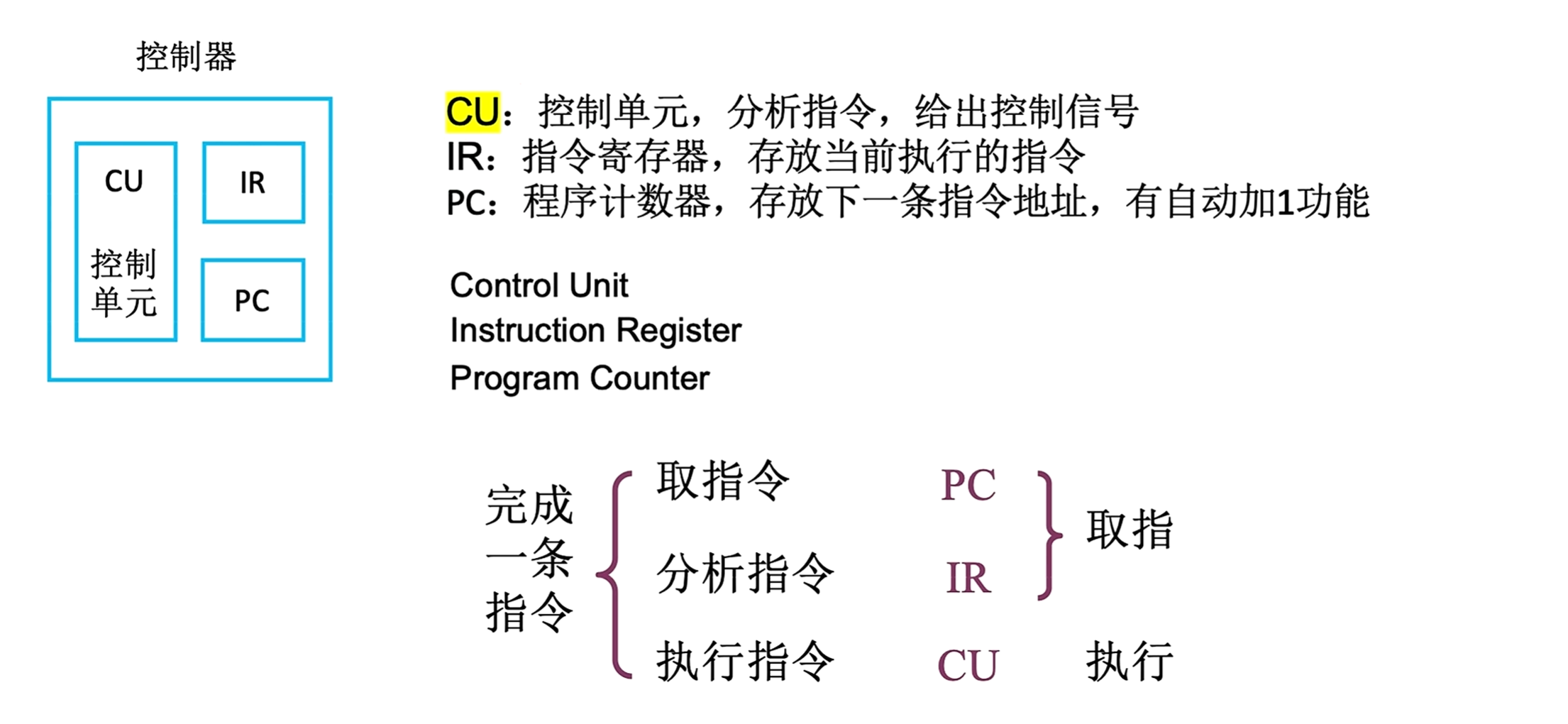

运算器 专用数据通路方式:根据指令执行过程中的数据和地址流动方向安排连接线路 内部单总线方式:将所有寄存器的输入端和输出端都连接到一条公共的通路上。 控制器 PC的位数取决于 存储器容量和指令字长(用字节编址和字编址) 字编址: == 存储器位数-log₂(指令字长字节数) ==CPU== ==四大部分:ALU,寄存器,中断系统,CU控制单元== ==本章重点:CU== 用户可见寄存器:PSW,ACC,PC,通用寄存器 用户不可见寄存器:IR,MAR,MDR,暂存寄存器,累加寄存器,移位寄存器 CPU(运算器+控制器)的功能 CPU 运算器 控制器 指令控制 对数据进行加工 取指令 操作控制 分析指令 时间控制 执行指令 数据加工 中断处理 中断处理

2026-03-02

计组-5.2 指令执行过程

指令执行过程指令周期 指令周期:CPU从主存中每取出并执行一条指令所需的全部时间 机器周期:==指令有多少步,就有几个机器周期。==分为 定长机器周期 和 不定长机器周期。又callCPU周期。 时间周期:即节拍,是CPU的最基本操作单位。 ==时间周期是出厂设定好的(主频倒数),但是不同的CPU的时间周期有长有短。== 每个指令周期内的机器数可以不等,每个机器周期内的节拍数也可以不等。 指令完整周期:取值 – (间址) – 执行 – (中断)周期。 四个工作周期都可以有CPU访存的操作。 CPU区分指令/数据的依据是:指令周期的不同阶段 指令完整周期 /...

2026-03-05

计组-5.4 微程序控制器

5.4 微程序控制器 一、基本原理==设计思路== 一条机器指令对应一个微程序 一个微程序有多条微指令(微周期,通常为一个机器周期) 一条微指令可以做多个微操作(微命令)(构成控制序列的最小单位) 基本结构CU的输入信号来源: ①译码器产生的指令信息 ②时序系统产生的节拍信号 ③执行单元的反馈信息(标志) 工作原理⭐ 一条机器指令 == 一个微程序 一条机器指令 的执行过程 = 取指微程序(入口地址一般为CM的0号单元) + 执行微程序(不同指令微程序不同) 微程序个数 = 机器指令数 + 取址,间址,中断周期的公共微程序数。 ①执行取指操作(公共) 启动取指: 机器开始运行时,自动将取指微程序入口地址(通常为CM的0号单元)送入μPC,并开始从CM中读取并执行取指微指令。 取指完成:...

2026-03-03

计组-5.3 数据通路的功能和基本结构

5.3 数据通路的功能和基本结构CPU内部可视为:数据通路 和 控制部件...

2026-03-08

计组-5.5 异常和中断机制

5.5 异常和中断机制异常:CPU内部产生的意外事件 中断:CPU外部的设备向CPU发出的中断请求 异常和中断的分类:异常: 硬故障中断 终止(Abort) 程序性异常(软件中断) 故障(Fault):在引起故障的指令启动后,执行结束前被检测到的异常事件。无法通过异常处理程序恢复故障,必须终止进程的执行。 自陷(Trap):预先安排的一种“异常”事件。 中断:可屏蔽中断 不可屏蔽中断 异常和中断的不同点: 一些异常(eg缺页溢出)是由特定指令在执行过程中发生的。而中断不和任何指令相关联,也不阻止任何指令的完成。 异常的检测由CPU自身完成。对于中断,CPU必须通过中断请求线获取中断源的信息,才能知道哪个设备发生了何种中断。 异常和中断的相应过程: 关中断 保存断点和程序状态 识别异常和中断并转到相应的处理程序 异常大多使用软件识别的方式:CPU设置一个异常状态寄存器,用于记录异常原因。 中断可以采用软件识别和硬件识别的方式:又称向量中断。

评论