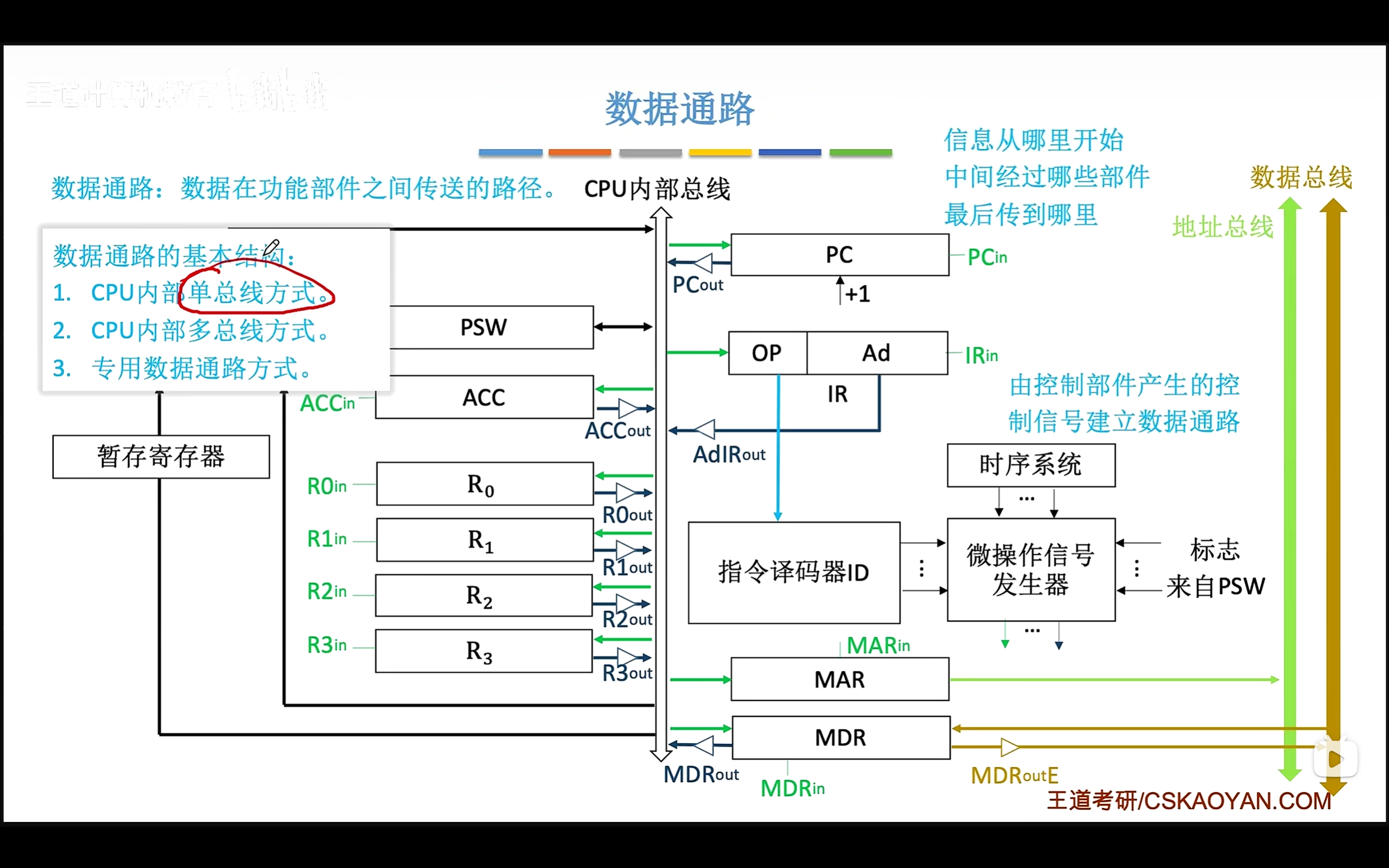

计组-5.3 数据通路的功能和基本结构

5.3 数据通路的功能和基本结构

CPU内部可视为:数据通路 和 控制部件 两大部分。

数据通路:数据在功能部件之间传送的路径。

CPU内数据的流动

- 寄存器和寄存器

- 寄存器和主存

- 寄存器和ALU

==数据通路的基本结构==

CPU内部单总线方式:CPU内数据通过一条总线传输。(常搭配多周期处理器,CPI>1)

CPU内部多总线方式:(常搭配单周期处理器,CPI=1)

专用数据通路方式:寄存器之间有通路来传输交流数据。

其他:

有总线时信号流动的原则:每个时刻只有一个器件发出信息,可以有多个器件接收消息。

CPI:每周期指令数。

- ==单周期处理器==:所有指令的指令周期为一个时间周期(all步骤,一个时间周期搞定)(==不同于单总线==哦)

- 在执行同一条指令的过程中,每个主要的硬件部件(如ALU)最多被使用一次。

- ==单周期处理器==:所有指令的指令周期为一个时间周期(all步骤,一个时间周期搞定)(==不同于单总线==哦)

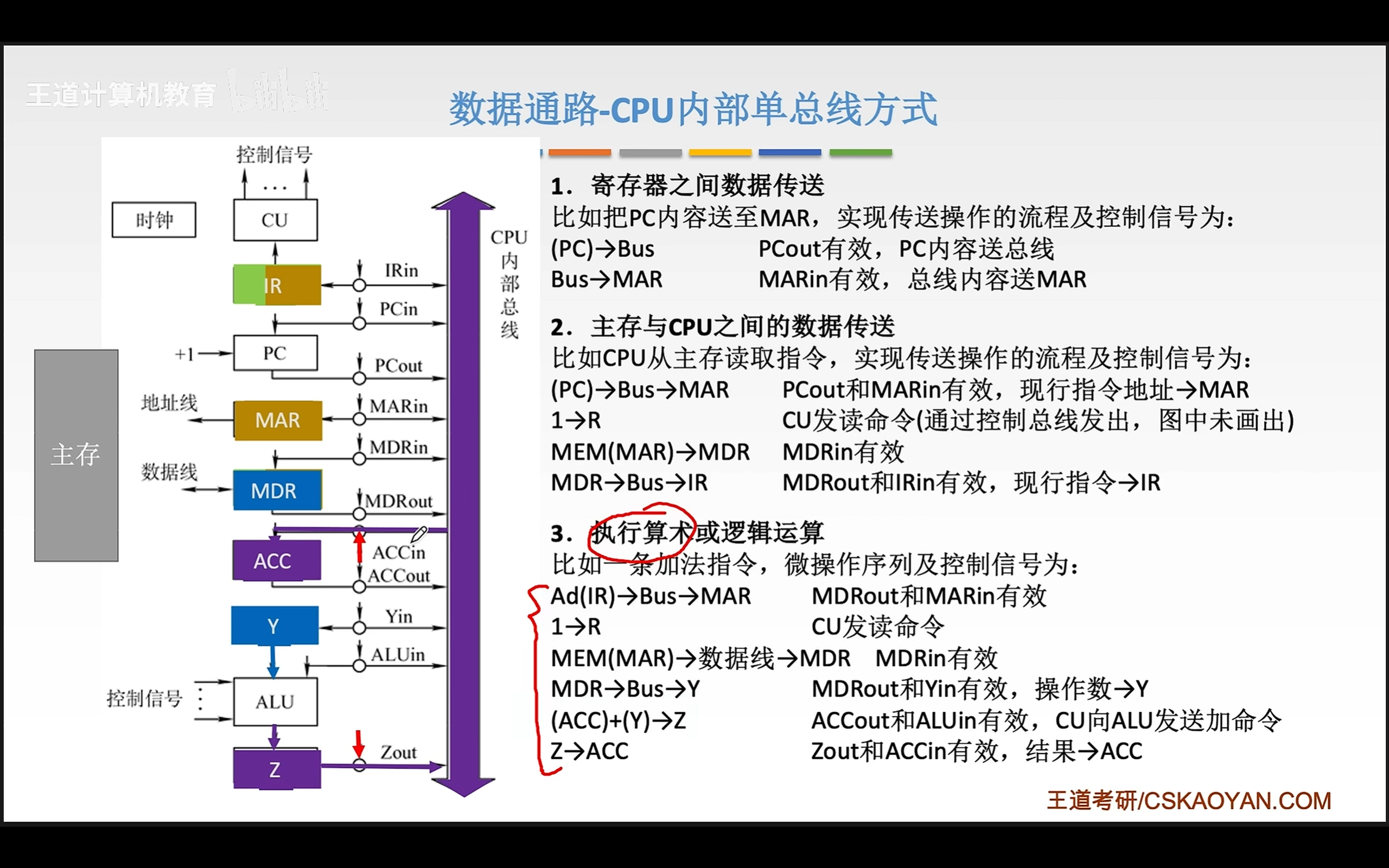

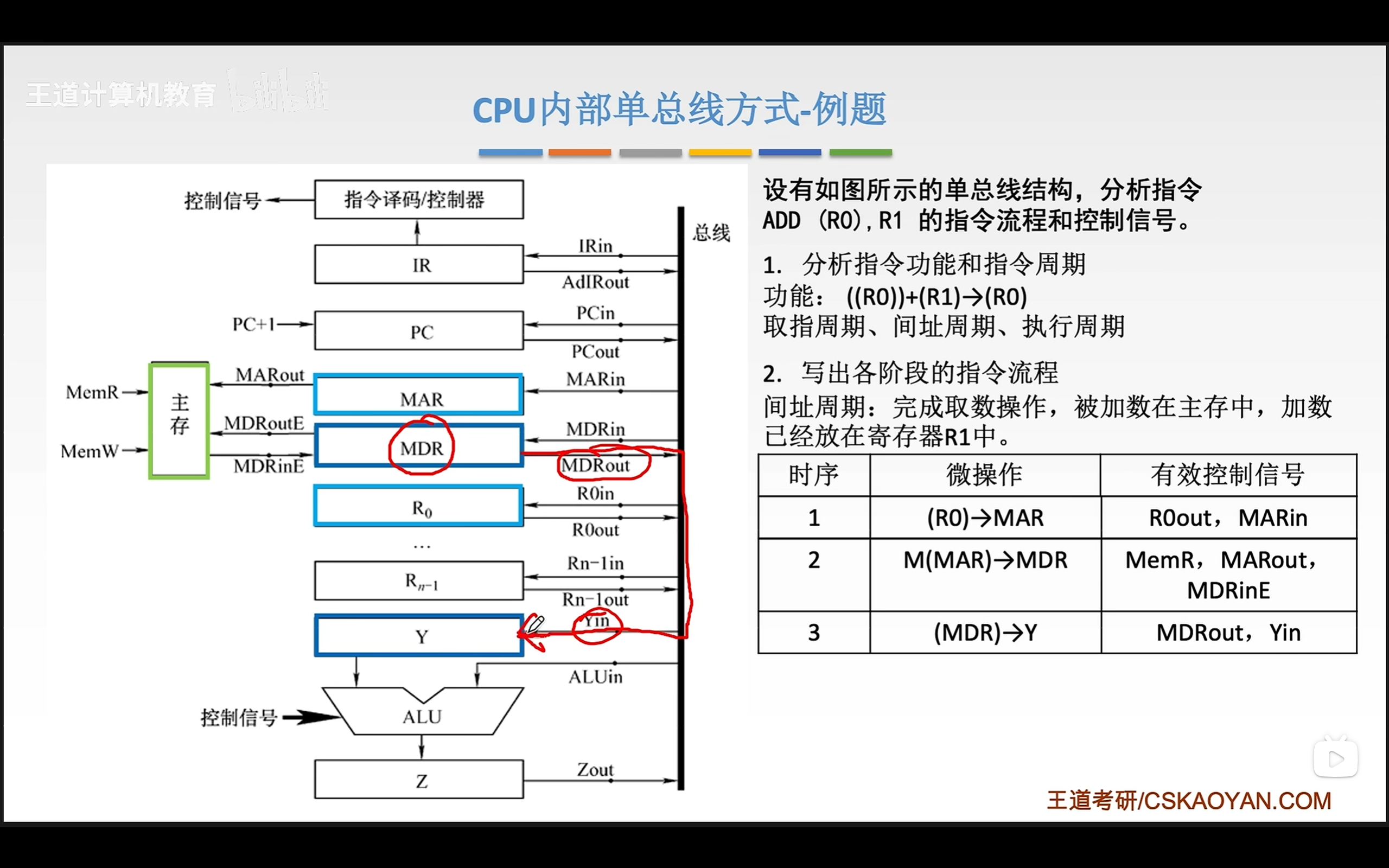

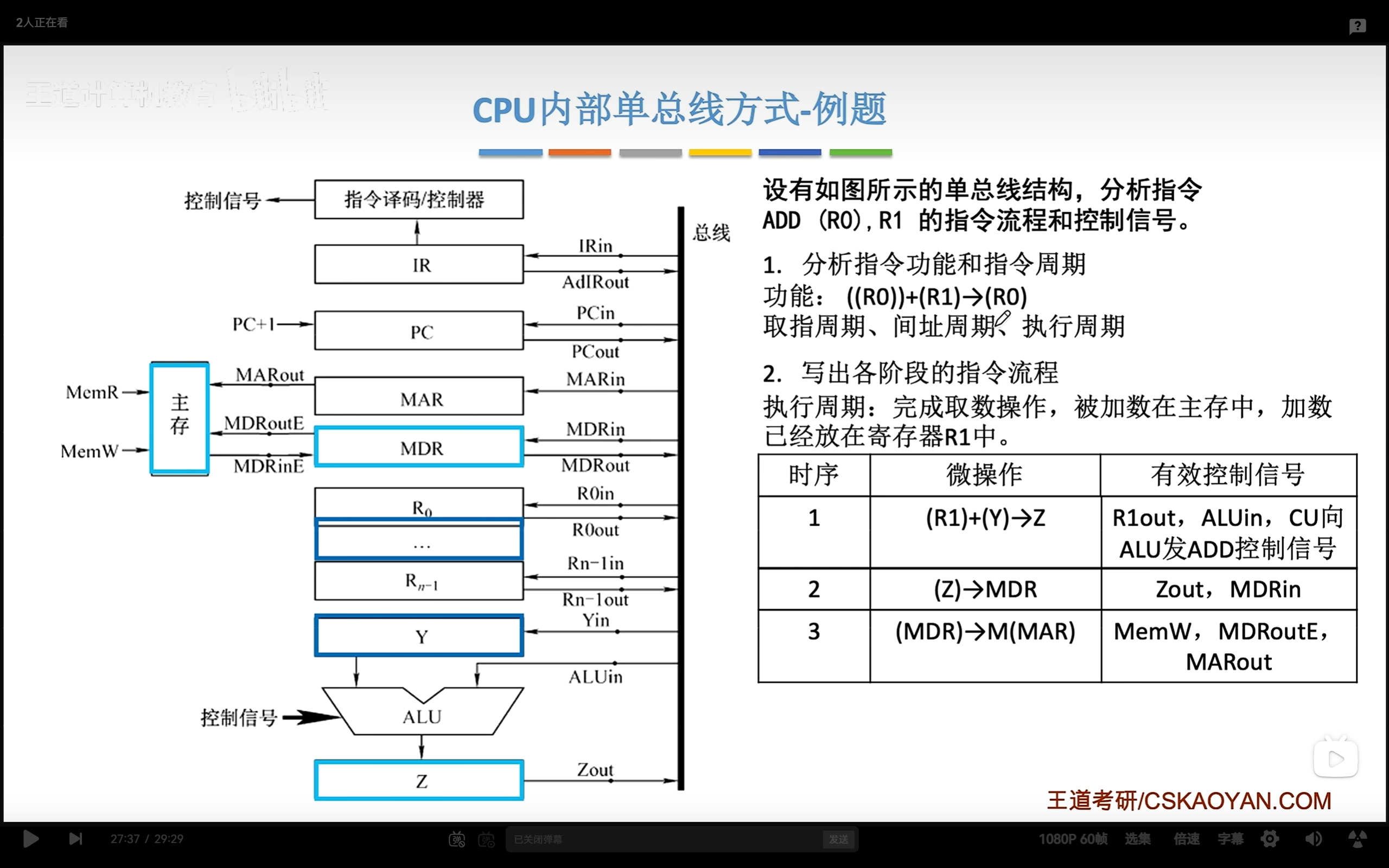

CPU内部单总线方式

- 每一个时钟周期,CU都会发出==一个==控制信号,执行完成==一个==微操作。

- 单总线结构中,每一时刻总线上只有一个数据有效

- ALU计算得配合暂存寄存器使用:另一个操作数提前放在暂存寄存器Y。

- MARinE(表示数据总线(到MARin这条路)是否畅通)

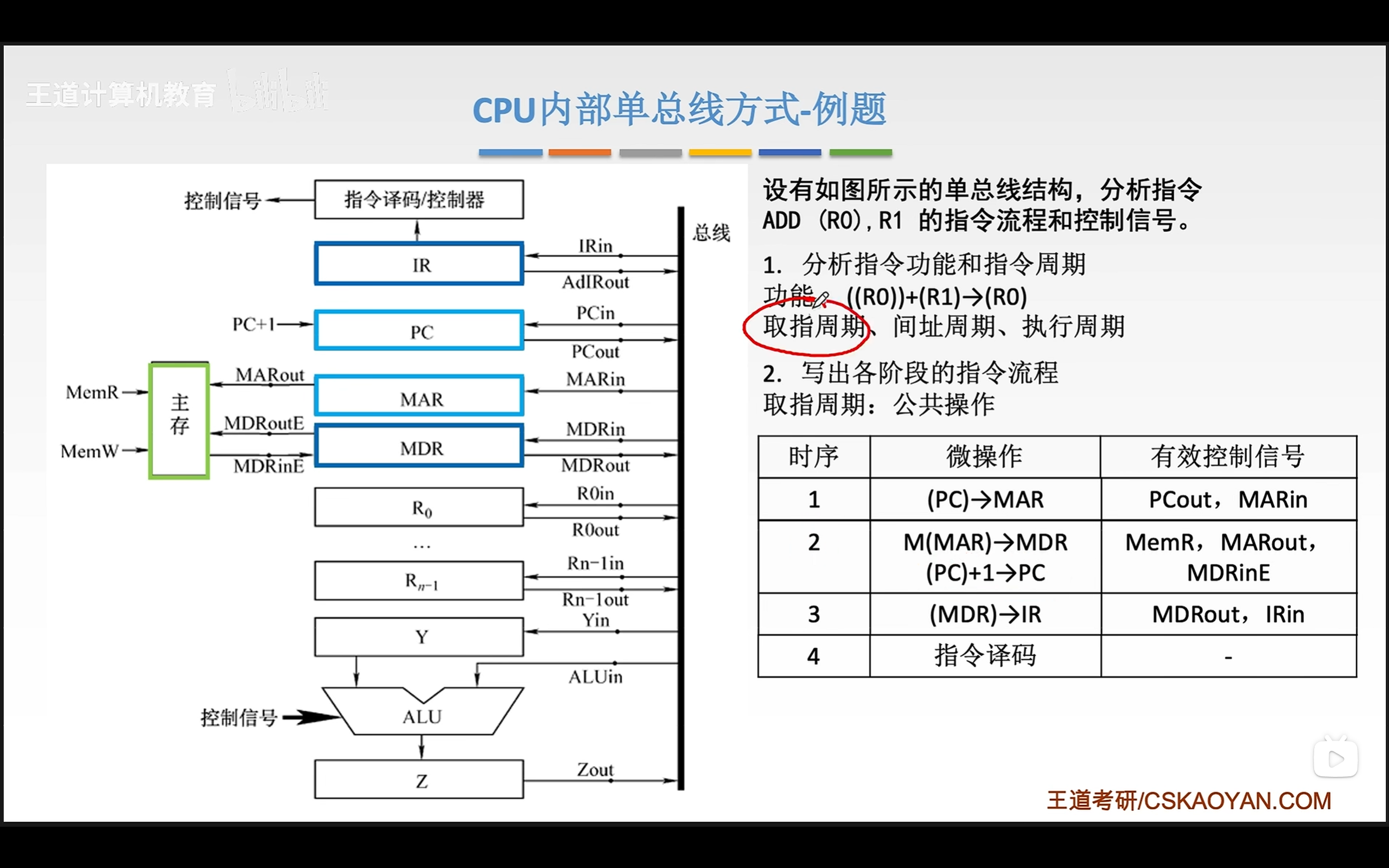

例题

- ALU不是寄存器(所以不写在上面,直接写Z就行)

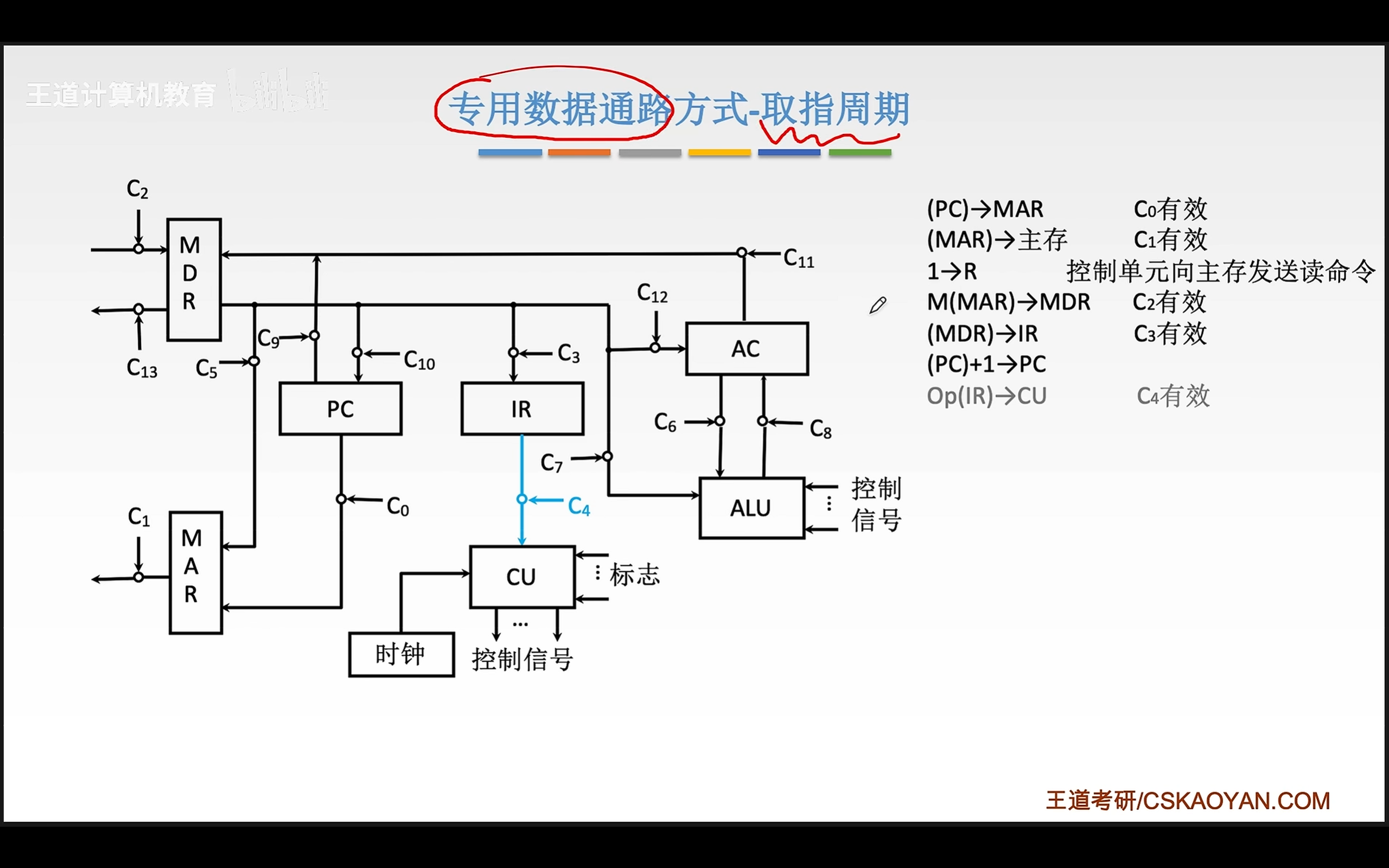

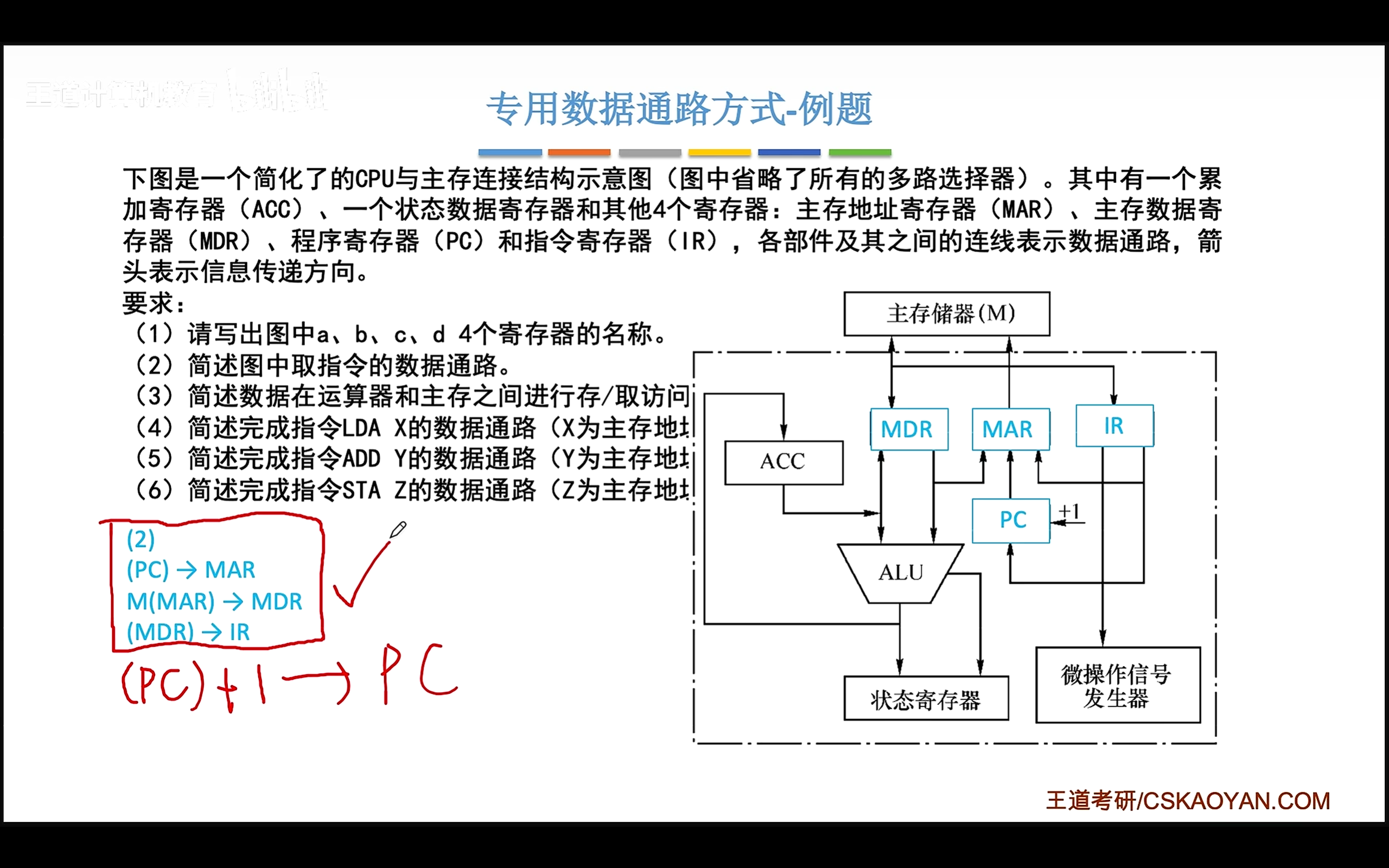

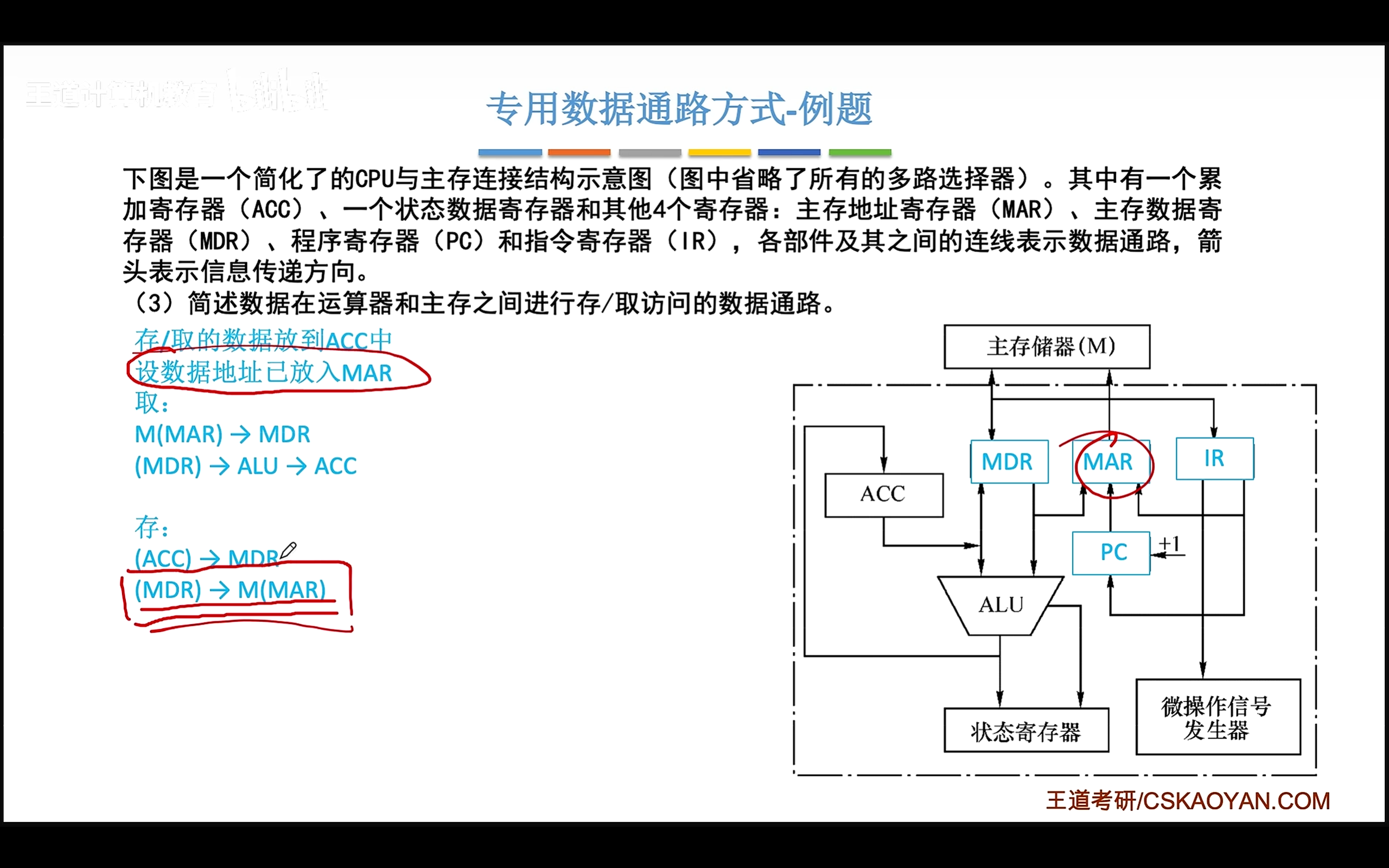

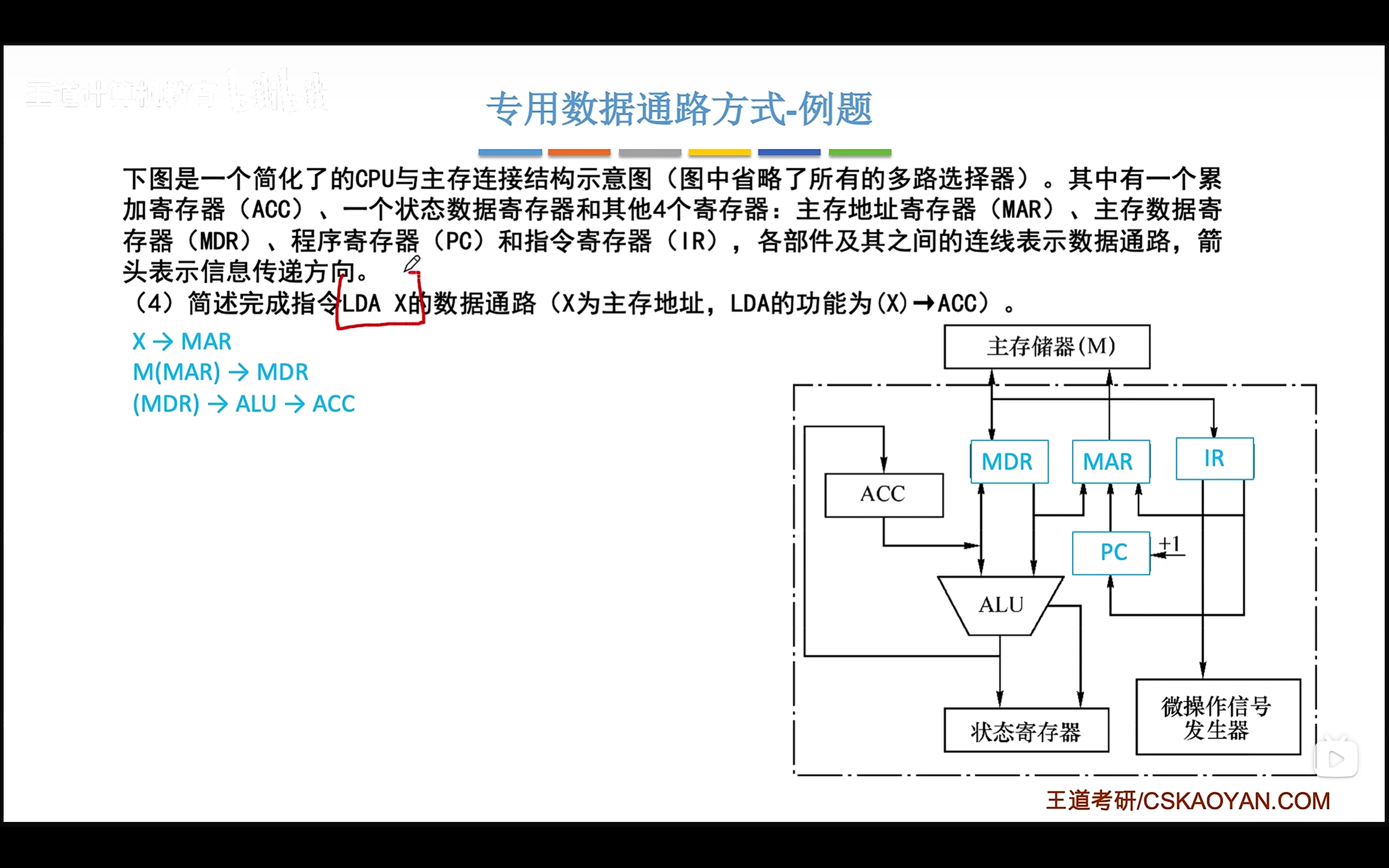

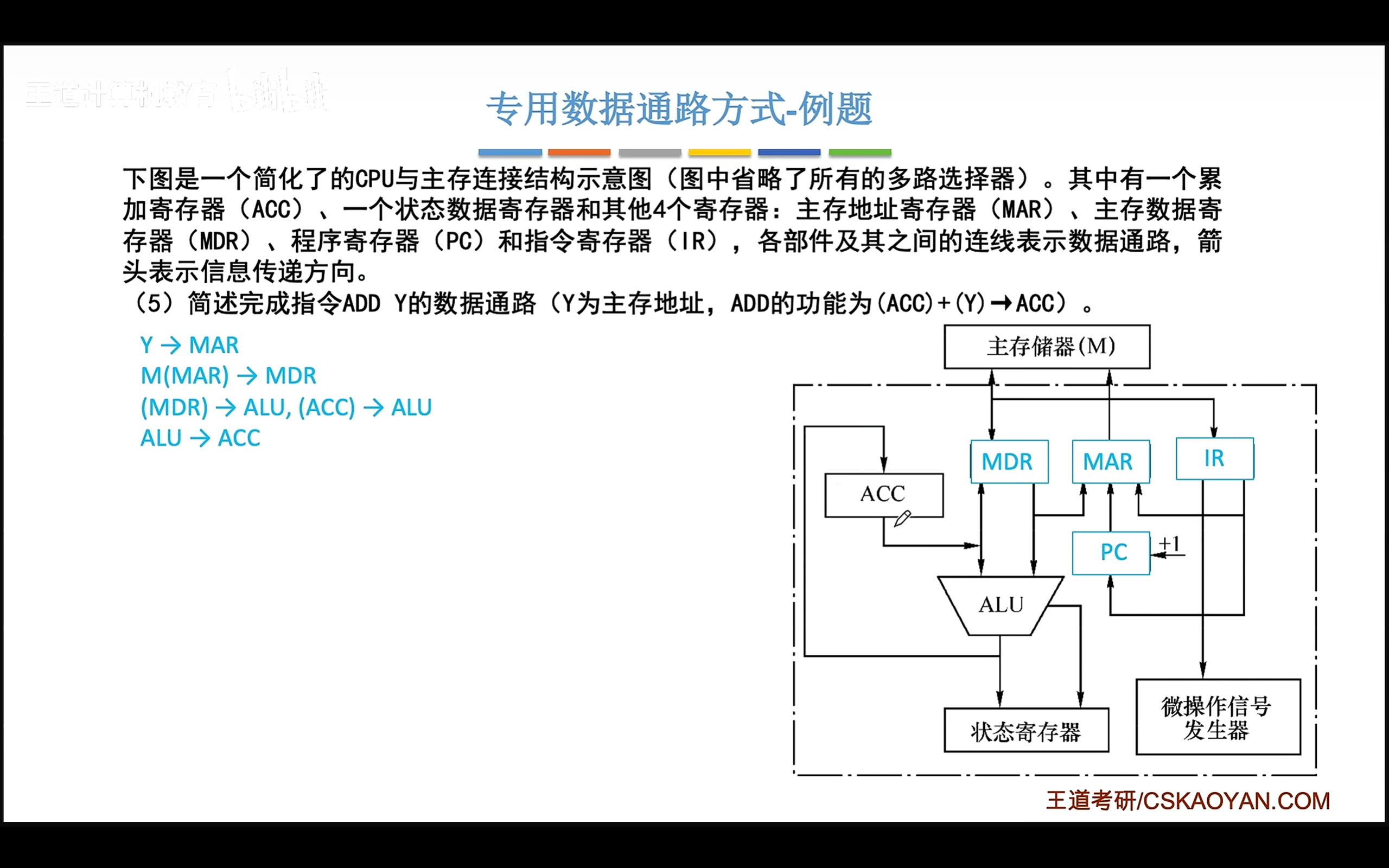

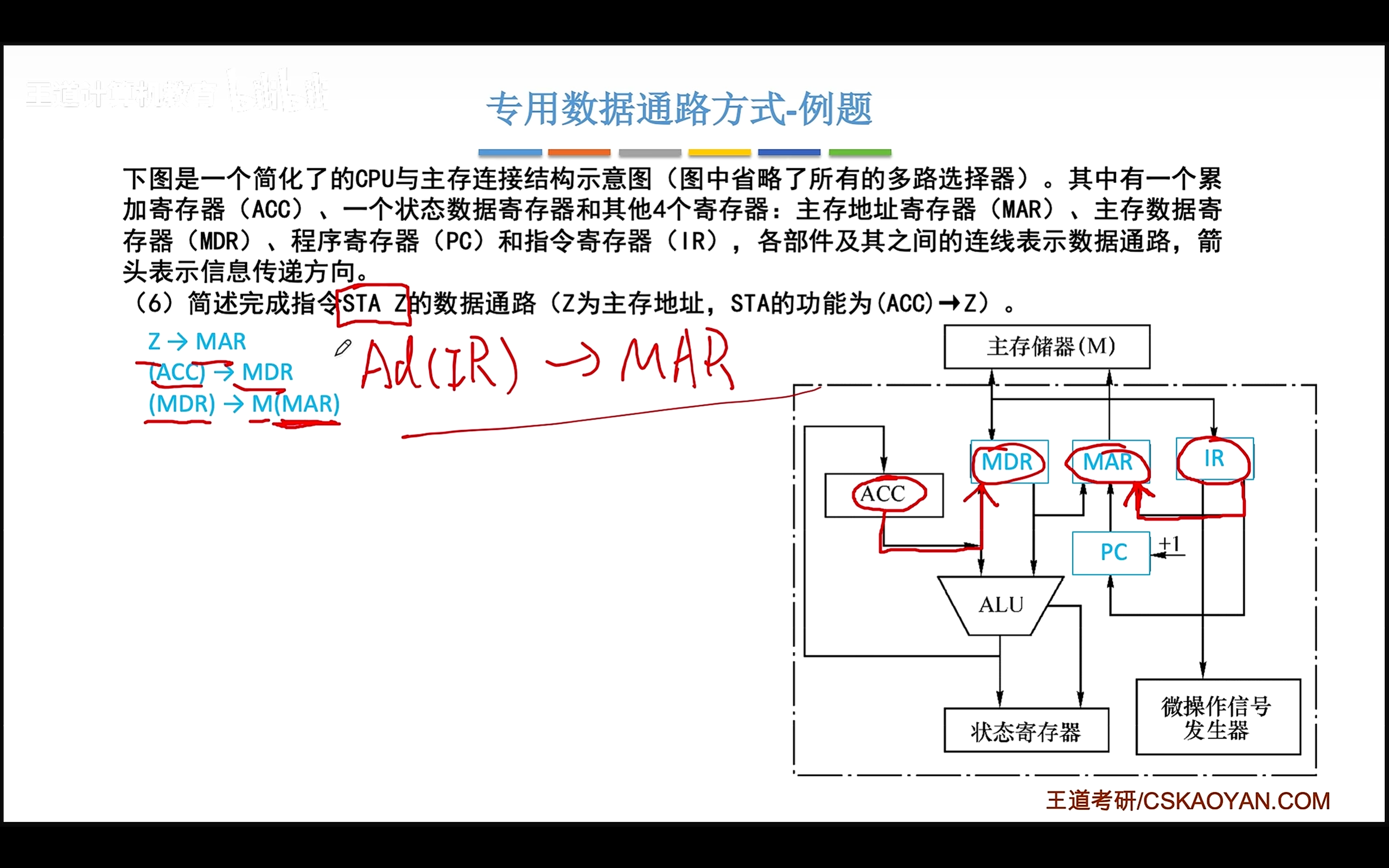

专用数据通路方式

- (指令译码器在微操作发生器里面)

例题

评论